# Predictive Control Scheme of the PMSM with a Modulator of Variable Switching Frequency

Von der Naturwissenschaftlich-Technischen Fakultät der Universität Siegen

Zur Erlangung des akademischen Grades

Doktor der Ingenieurswissenschaften

(Dr.-Ing.)

genehmigte Dissertation

von

M. Sc. Fernando David Ramirez Figueroa aus Tlalnepantla de Baz, Mexiko

1. Gutachter: Prof. Dr.-Ing. Mario Pacas

2. Gutachter: Prof. Dr.-Ing. Ralph Kennel

Tag der mündlichen Prüfung: 07.03.2017

# Acknowledgements

The present work was realized during my research activities at the Institute of Power Electronics and Electrical Drives of the University of Siegen. It was carried out thanks to the financial support of the German Academic Exchange Service (Deutscher Akademischer Austauschdienst - DAAD) and the Mexican National Council on Science and Technology (Consejo Nacional de Ciencia y Tecnología – CONACYT) under the scholarship "CONACYT-DAAD 2012."

First, I would like to express my deepest gratitude to my supervisor and head of the institute Prof. Dr.-Ing. Mario Pacas, for allowing me to be part of his working group and his unconditional support during my doctoral studies. I would also like to thank Prof. Dr.-Ing. Ralph Kennel of the Technische Universität München for his interest in my and his work as co-examiner. Moreover, I would like to thank my colleagues Dr.-Ing. Simon Feuersänger and Dr.-Ing. Manuel Steinbring for their support and vital help.

Furthermore, I would like to express my appreciation and gratitude to the personnel of the Institute for always providing a friendly and supportive working environment. I would like to mention Dipl.-Ing. Erhard Oerter and Mrs. Sabine Leukel for the great technical and administrative assistance. The time I spent working at the institute was an invaluable learning experience as well as the origin some great memories.

Special thanks to Ismael and Victor, for their great friendship and support has always that made a great difference. To my sister Carolina, for bringing me close to the family and home during the moments that I most need it, without her even knowing it. To Anna Maria for all her support on the final phase of my doctoral studies. Finally, I would like to thank my parents, Virginia and Fernando for all their unconditional support and love ever since their brought me to life.

Fernando David Ramirez Figueroa

# Contents

| Contents                                                          | I   |

|-------------------------------------------------------------------|-----|

| Abstract                                                          | i   |

| Zusammenfassung                                                   | iii |

| Nomenclatures                                                     | 1   |

| 1 Introduction                                                    | 5   |

| 1.1 Motivation                                                    | 5   |

| 1.2 Objectives                                                    | 6   |

| 1.3 State of the Art                                              | 7   |

| 1.3.1 Variable Switching Frequency                                | 7   |

| 1.3.2 Sensorless Control                                          | 8   |

| 1.3.3 Model-based Predictive Control                              | 9   |

| 1.3.4 FPGA-based Control Schemes for Power Electronics and Drives | 11  |

| 1.4 Outline of the Chapters                                       | 14  |

| 2 Theoretical Fundamentals                                        | 15  |

| 2.1 The Space Phasor                                              | 15  |

| 2.1.1 Fixed α,β-Coordinate System                                 | 16  |

| 2.1.2 Rotating d,q-Coordinate System.                             | 18  |

| 2.1.3 Coordinate Transformations                                  | 18  |

| 2.2 Permanent Magnets Synchronous Machine                         | 19  |

| 2.2.1 Permanent Magnets for Electrical Machines                   | 20  |

| 2.2.2 Permanent Magnets Rotor Types                               | 21  |

| 2.2.3 Modeling of the PMSM                                        | 22  |

| 2.3 Voltage Source Inverter                                       | 24  |

| 2.3.1 Generation of the Voltage Space Phasors                     |     |

| 2.4 Space Phasor Modulation                                       | 26  |

| 2.5 Field Oriented Control Principle                              | 28  |

| 2.6 Model-based Predictive Control Principle                      | 30  |

| 2.6.1 Defining the Cost Function                                  | 31  |

| 2.6.2 Optimization of the Controller Output                       |     |

| 2.6.3 Finite-Set MPC Current Controller                           |     |

| 2.7 Summary of the Chapter                                        |     |

| 3 FPGA-Based Controller Design for PMSM Drives                    | 36  |

| 3.1 FPGA General Structure                                        | 36  |

#### Contents

| 3.2 Digital Signal Processing using FPGAs                                         | 38         |

|-----------------------------------------------------------------------------------|------------|

| 3.2.1 Advantages of using FPGAs                                                   | 38         |

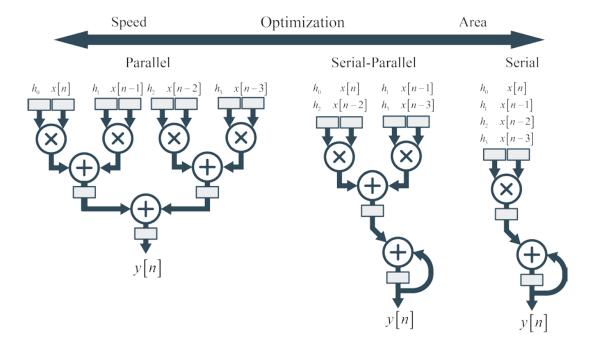

| 3.2.2 Speed vs Area Optimization Methods                                          | 41         |

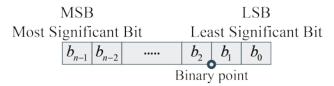

| 3.2.3 Fixed-Point Number Representation                                           | 42         |

| 3.3 CORDIC Algorithm                                                              | 42         |

| 3.4 Delta-Sigma Analog-to-Digital Conversion                                      | 45         |

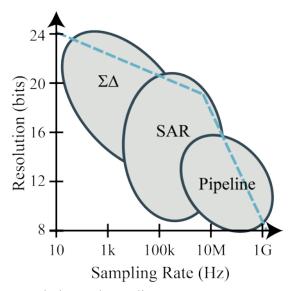

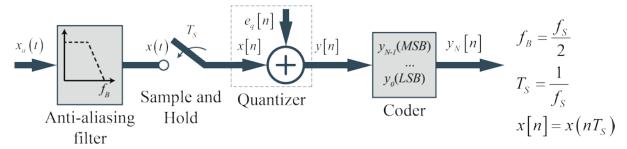

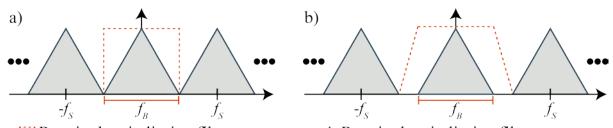

| 3.4.1 Basics of Analog-to-Digital Conversion                                      | 45         |

| 3.4.2 Delta-Sigma Analog-to-Digital Converters                                    | 49         |

| 3.5 Hardware Description Languages (HDL)                                          | 54         |

| 3.6 FPGA-based Controller Design.                                                 | 55         |

| 3.6.1 Development and Optimization Cycle of the Control Scheme                    | 57         |

| 3.7 Summary of the Chapter                                                        | 58         |

| 4 Predictive Control of the PMSM with a Modulator of Variable Switching Frequency | <b> 60</b> |

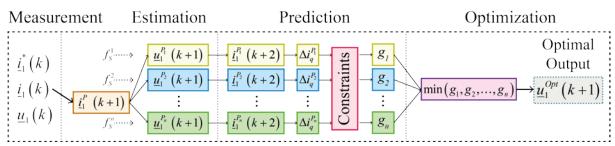

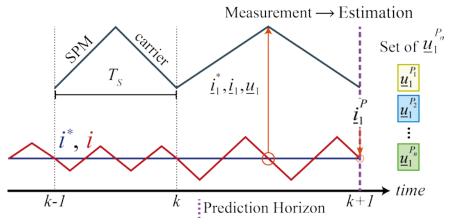

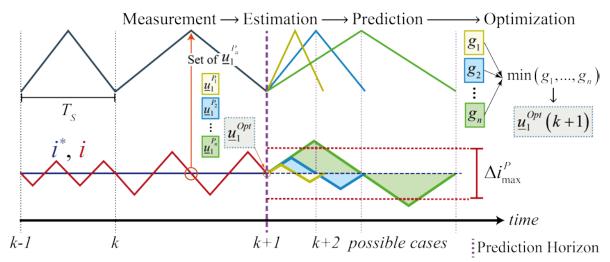

| 4.1 Control Strategy                                                              | 61         |

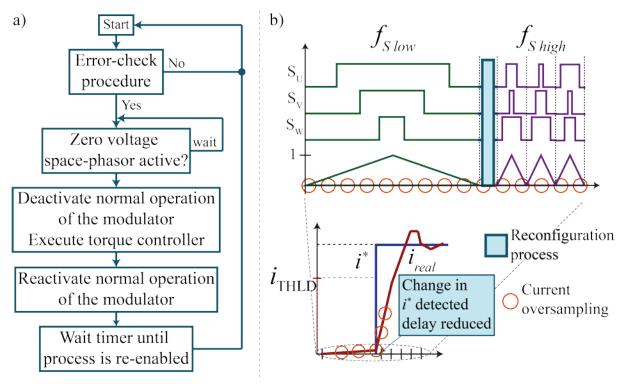

| 4.1.1 Operation Principle                                                         | 64         |

| 4.2 Predictive Torque Control Approach                                            | 64         |

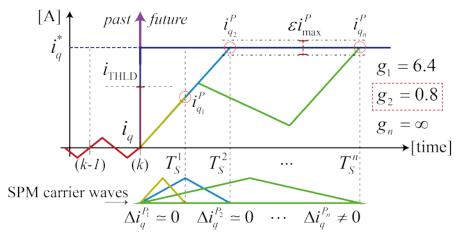

| 4.2.1 The Cost Function                                                           | 66         |

| 4.2.2 Estimation of the Current Space Phasors                                     | 69         |

| 4.2.3 Voltage References                                                          | 70         |

| 4.2.4 Estimation of the Electromagnetic Torque                                    | 72         |

| 4.2.5 Implementation of the proposed FPGA-based Control                           | 79         |

| 4.2.6 Optimization of the Proposed Control Scheme                                 | 82         |

| 4.2.7 Reconfigurable Pulse-width Modulation Unit                                  | 85         |

| 4.3 Sensorless Control                                                            | 89         |

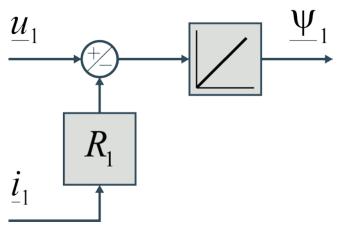

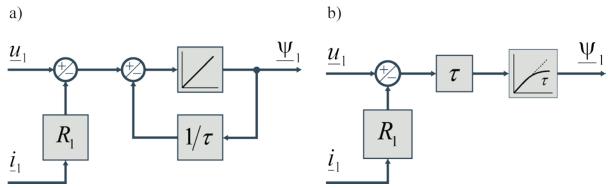

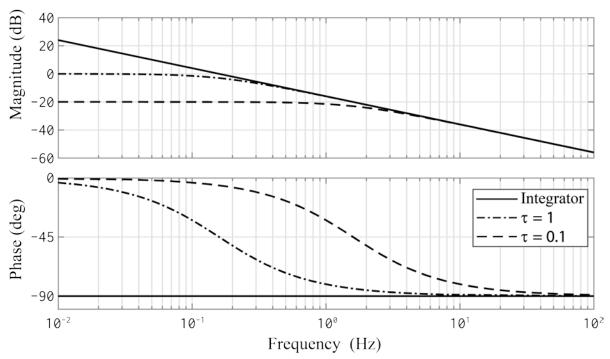

| 4.3.1 Fundamental Wave Models                                                     | 89         |

| 4.3.2 Sensorless Control at Low-Speed Range without Signal Injection              | 92         |

| 4.4 Summary of the Chapter                                                        | 96         |

| 5 Experimental Results                                                            | 98         |

| 5.1 Experimental Setup                                                            | 98         |

| 5.2 Predictive Control with Variable Switching Frequency                          | 100        |

| 5.2.1 Current Response against conventional FOC in Standstill                     | 100        |

| 5.2.2 Reconfiguration of the Pulse-width Modulation Units in Detail               | 105        |

| 5.2.3 Speed Control Mode                                                          | 107        |

| 5.2.4 Enhanced Current Ripple Estimation                                          |            |

| 5.3 Sensorless Control                                                            | 126        |

| 5.3.1 Sensorless Control at High-Speed Ranges                                     | 126        |

## Contents

| 5.3.2 Sensorless Control at Low-Speed Ranges | 128 |

|----------------------------------------------|-----|

| 6 Conclusions                                | 135 |

| A Machine Parameters                         | 138 |

| B Switching Frequency Values                 | 139 |

| Bibliography                                 | 140 |

#### **Abstract**

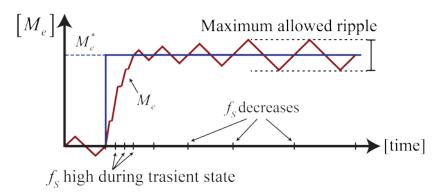

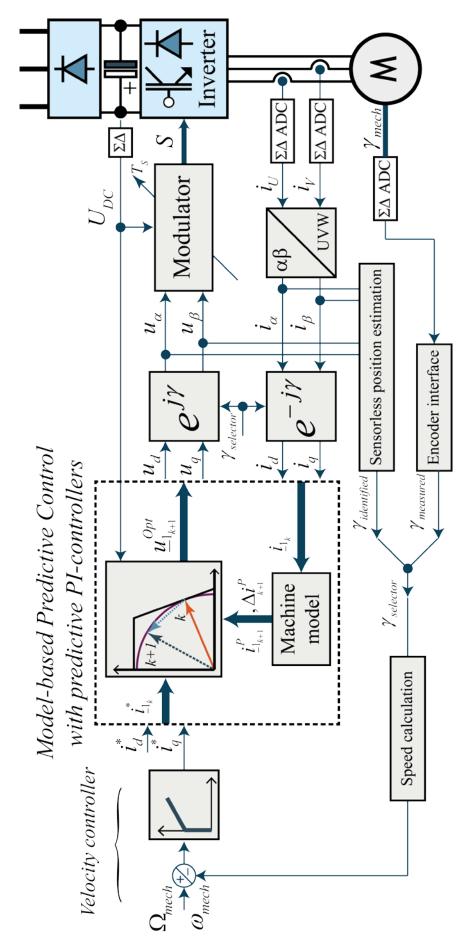

In this work, a novel predictive control scheme for the permanent magnet synchronous machine by using a pulse-width modulation technique of variable switching frequency and variable sampling time is proposed. The control scheme is based on the model-based predictive control theory and makes use of a flexible pulse width modulation stage that can be reconfigured during the operation of the system without stopping the execution.

The PI-controllers conventionally used in field-oriented control schemes are modified so that they can be used during the prediction stage of the control with different sampling times, without saturating the integral part of the controller. A finite set of switching frequencies is used for the optimization of a cost function, which aims to minimize not only the error in the torque and flux producing components of the currents of the space phasor of the PMSM. In addition, the cost function includes the reduction of the switching losses by directly reducing the switching frequency and maintaining a minimum level of desired performance mainly regulated by the maximum allowed torque ripple. The oversampling of the reference signals allows the adaption of the sampling frequency in order to avoid delays in the reaction of the system in case of transients.

The proposed control scheme demands a high degree of flexibility in the implementation and a fast signal processing. Therefore, a FPGA implementation was mandatory that allows the realization of most of the control algorithm in silicon and a parallel execution. The acquisition of analogue control signals is carried out by means of Delta-Sigma ADCs with a very short conversion time that permits an oversampling and a signal processing with a high time resolution. As a result, the control features not only an excellent dynamic behavior with high bandwidth allowing to consider the harmonics of the current i.e. the switching ripple.

The proposed predictive control approach, successfully overcomes the majority of the drawbacks of conventional field-oriented control and eliminates some of the drawbacks of conventional model predictive control, delivers good dynamics in the torque behavior and exploits the parallel processing capabilities and high computational power provided by an FPGA implementation. A sensorless implementation complements the proposed predictive control strategy. The faster processing capabilities

of the FPGA allow the sensorless operation of the drive at very low speeds without the need of additional signal injection.

# Zusammenfassung

Die vorliegende Arbeit befasst sich mit der prädiktiven Regelung einer permanenterregten Synchronmaschine mit Pulsweitenmodulation und variabler Schaltfrequenz. Das vorgestellte Regelkonzept nutzt eine Modell basierte prädiktive Regelung wobei eine Pulsweitenmodulation verwendet wird, die während des Betriebs rekonfiguriert werden kann. Konventionelle, digitale PI-Regler, die auch in der feldorientieren Regelung Verwendung finden, werden während der Prädiktionsphase mit verschiedenen Abtastzeiten so modifiziert, dass es zu keiner Sättigung der Regler kommt.

Mittels einer begrenzten Anzahl von Schaltfrequenzen kann die Kostenfunktion optimiert werden. Die zu minimierende Kostenfunktion beinhaltet unter anderem das Drehmoment und die flussbildende Komponente des Raumzeigers der permanenterregten Synchronmaschine. Während der Minimierung können die Schaltverluste reduziert werden, wobei eine minimal geforderte Dynamik erhalten bleibt, welche in der Regel durch die maximal erlaubte Drehmomentwelligkeit begrenzt wird. Die Überabtastung der Sollwerte erlaubt die Adaptierung der Schaltfrequenz während transienter Vorgänge um die Verzögerung in der Reaktion des Systems zu reduzieren.

Das vorgeschlagene Regelungsverfahren erforscht eine hohe Flexibilität und eine schnelle Signalverarbeitung, wodurch die Implementierung erfolgt darum mittels eines FPGAs. Die meisten notwendigen Regelungsalgorithmen werden in Silizium ausgeführt und parallel verarbeitet. Die Messdatenerfassung der analogen Signale wurde mittels Delta-Sigma ADCs durchgeführt, die eine sehr kurze Umsetzungszeit haben und damit die Überabtastung der Signale mit höherer zeitlicher Auflösung ermöglichen. Als Ergebnis hat das vorgeschlagene Regelungsverfahren ein hervorragendes dynamisches Verhalten mit hoher Bandbreite, wodurch die Berücksichtigung von Harmonischen möglich wird.

Der vorgeschlagene Ansatz der prädiktiven Regelung eliminiert einen Großteil der Nachteile der herkömmlichen feldorientierten Regelung sowie einige der Nachteile der gewohnten modellprädiktiven Regelung. Insbesondere wird eine gute Dynamik im Drehmomentverhalten erreicht, wobei die parallele Verarbeitungsmöglichkeit und hohe Rechenleistung durch die FPGA-Implementierung ausgenutzt wird. Eine sensorlose Implementierung vervollständigt das vorgestellte prädiktive Regelungsverfahren. Die

hohe Rechenleistung des FPGAs erlaubt den sensorlosen Betrieb des Antriebs bei niedrigen Geschwindigkeiten ohne zusätzliche Signaleinprägung.

# Nomenclatures

# Symbols

| o           | Degrees, which unless otherwise noticed, mean electrical degrees |

|-------------|------------------------------------------------------------------|

| x           | Absolute value of <i>x</i>                                       |

| C           | Capacitor, Constant                                              |

| $clk_{DSP}$ | DSP execution clock                                              |

| clkfpga     | FPGA execution clock                                             |

| D           | Diode, down-sampling or decimation filter, duty-cycle            |

| d,q         | Rotor-flux oriented reference frame                              |

| e<br>e      | Error                                                            |

| f           | Frequency                                                        |

| $f_B$       | Bandwidth frequency                                              |

| $f_D$       | Decimation frequency                                             |

| fpen        | Penalizing function                                              |

| $f_N$       | Nyquist-rate sampling frequency                                  |

| $f_S$       | Switching frequency, sampling frequency                          |

| g           | Cost function                                                    |

| i           | Current                                                          |

| Im          | Imaginary part                                                   |

| j           | Constraint                                                       |

| J           | Moment of inertia                                                |

| K           | CORDIC scaling factor                                            |

| $K_f$       | Sum of the CORDIC scaling factor during different iterations     |

| $K_I$       | Integral controller gain                                         |

| $K_P$       | Proportional controller gain                                     |

| L           | Inductance                                                       |

| M           | Torque, decimation ratio                                         |

| $M_e$       | Electromagnetic Torque                                           |

| $M_L$       | Mechanical Load Torque                                           |

| N           | N steps ahead prediction horizon                                 |

| p           | Pair of Poles                                                    |

| R           | Resistance                                                       |

| Re          | Real part                                                        |

| S           | Ideal switch (power semiconductor)                               |

| t           | Time                                                             |

| T           | Transistor                                                       |

| $T_D$       | Dead-time                                                        |

| $T_E$       | Execution time                                                   |

| $T_P$       | Positive-phase switch                                            |

| $T_N$       | Integration time constant, negative-phase switch                 |

| $T_S$       | Sampling time, switching period, modulation period               |

u, UVoltage, phase U DC-link voltage  $U_{DC}$ UVWThree-phase AC system VPhase V WPhase W w Weight factor Stator-fixed coordinate system  $\alpha,\beta$ Difference operator, switching ripple,  $M_e$  ripple, quantization step Δ Angle between the  $\alpha$ -axis and the rotor flux-oriented reference frame γ Duty-cycle or power-on time within a period λ Microcontroller μC Flux linkage Ψ Angular speed  $\omega$

## **Subscripts**

Ω

Mechanical speed

| Stator quantity                                                       |

|-----------------------------------------------------------------------|

| Rotor quantity                                                        |

| Real part of a space phasor in a <i>d</i> , <i>q</i> -reference frame |

| Limit                                                                 |

| Maximum value                                                         |

| Mechanical                                                            |

| Nominal value, normalized value                                       |

| Imaginary part of a space phasor in a $d,q$ -reference frame          |

| Threshold limit value                                                 |

| Phase U                                                               |

| Phase V                                                               |

| Phase W                                                               |

| Real part of a space phasor in a stator-fixed reference frame         |

| Imaginary part of a space phasor in a stator-fixed reference frame    |

|                                                                       |

# Superscripts

| $x^*$      | Reference value                                                    |

|------------|--------------------------------------------------------------------|

| $\dot{x}$  | Time derivative                                                    |

| $\hat{x}$  | Estimated, predicted value                                         |

| $x^{dist}$ | Disturbance value                                                  |

| $x^n$      | <i>n</i> -element of the finite set of possible solutions (FS-MPC) |

| $x^N$      | Base value                                                         |

| $x^{Opt}$  | Optimal value                                                      |

| $x^P$      | Predicted, estimated value                                         |

#### Acronyms

ΔΣ Delta-Sigma (ADC)AC Alternating CurrentA/D Analog-to-Digital

AV Active Voltage space phasor ADC Analog-to-Digital Conversion

AlNiCo Aluminum (Al), Nickel (Ni) and Cobalt (Co)

ASIC Application Specific Integrated Circuit

CAD Computer-Aided Design

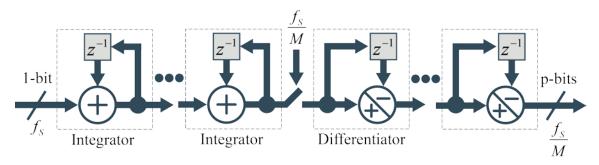

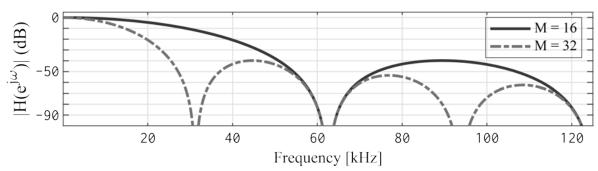

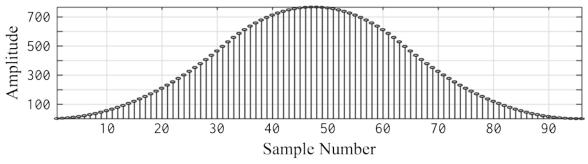

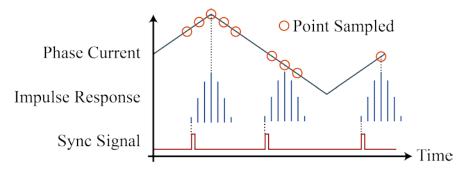

CIC Cascaded Integrator Comb Filter

CORDIC Coordinate Rotational Digital Computer

CS-MPC Continuous Set Model Predictive Control

DAC Digital-to-Analog Converter

DC Direct Current

DF Decimation Filter

DSP Digital Signal Processing, Digital Signal Processor

DTC Direct Torque Control

DMPC Direct Model-based Predictive Control EESM Electrically Excited Synchronous Machine

EMI Electromagnetic Interference

FOC Field Oriented Control

FS-MPC Finite Set Model-based Predictive Control

FPGA Field Programmable Gate Array

FIR Finite Impulse Response

GaN Gallium Nitrate

GPIO General Purpose Input Output (pin)GPC Generalized Predictive ControlHDL Hardware Description Language

THLD Threshold

IGBT Insulated Gate Bipolar Transistor

I/O Input / Output

INFORM Indirect Flux Detection by Online Reactance Measurement

LPF Low Pass Filter

LSB Least Significant Bit

LUT Look-Up Table

MBC Model-Based Control MBD Model-Based Design

MPC Model-based Predictive Control

MSB Most Significant Bit

MRAS Model Reference Adaptive System

NTF Noise Transfer Function

OpenCL Open Computing Language

OSR Oversampling Rate

#### Nomenclatures

PI Proportional Integral (controller)

PLL Phase Locked Loop PM Permanent Magnet

PMSM Permanent Magnets Synchronous Machine

PWM Pulse Width Modulation RAM Random Access Memory ROM Read Only Memory

RPWM Random Pulse Width Modulation

SAR Successive-Approximation

SiC Silicon Carbide SoC System-on-Chip SmCo Samarium-Cobalt

SPM Space Phasor Modulation

SNR Signal-to-Noise Ratio

STF Signal Transfer Function

THD Total Harmonic Distortion

VSI Voltage Source Inverter

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

ZV Zero Voltage space phasor

## 1 Introduction

Energy is the foundation of any technological development and as such the energy consumption in highly industrialized countries reflects how advanced is their technological development. Energy can be found in many forms, yet from the point of generation to the final point of utilization, the most effective way to transport it is converting it to electrical energy.

Another important form of energy is the mechanical one, which is needed in a wide spectrum of power ratings wherever manufacturing or production processes, transportation of persons or goods (among many others) take place, ultimately, electrical drives are well-suited electromechanical devices for the final conversion at the point of usage [1].

The research on the control of AC electrical drives was first limited by the available processing power, as microelectronics evolved and became more powerful, the implementation of more sophisticated and complex methods also became possible. Today, one of the most active research topics is the development of speed sensorless or encoderless AC drives featuring a dynamic behavior comparable to drives with a mechanical sensor on the shaft [2], [3]. Other very active research active topics deal with the enhancement of the control techniques like MPC [4] or artificial intelligence [5].

#### 1.1 Motivation

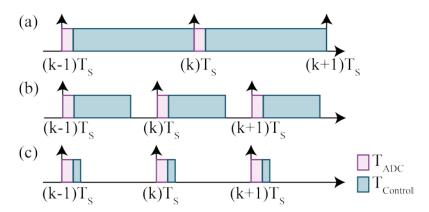

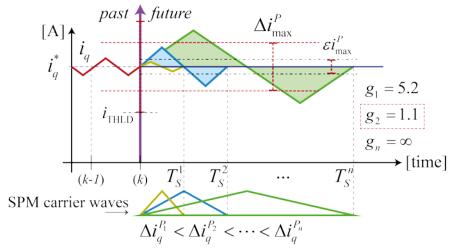

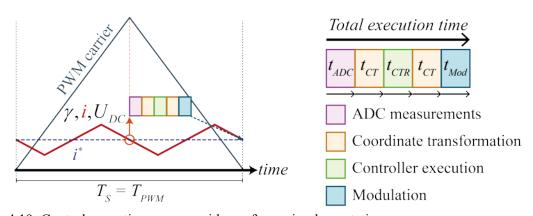

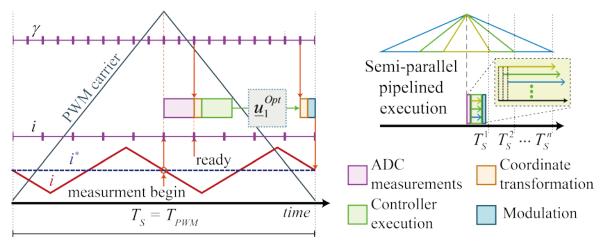

The motivation of this work is the enormous and continuously increasing processing capabilities made available by modern microelectronics. A classic example consists of the current control of pulse-width modulated inverters. As shown in Figure 1.1, by using modern digital electronics the processing time of the control algorithm has been dramatically reduced. In this figure,  $T_{ADC}$  is the analog-to-digital conversion time,  $T_{Control}$  the time it takes to execute the control algorithm and  $T_S$  is the sampling period usually equal to the switching period of the power converter, or half of it.

When a general-purpose microcontroller is used (Figure 1.1a) the main limitation factor is its computing power. The sampling period has to be adapted to this limit leading to a reduced bandwidth of the closed-loop system. Figure 1.1b depicts the case of a DSP used for the implementation. These components allow the execution of the control

algorithm in a few dozens of microseconds. Thus, the speed of the controller is no longer a restriction of the closed-loop system. The limitations of the sampling time are based on the switching losses of the power converter.

Finally Figure 1.1c, corresponds to an FPGA-based controller, due to their potential to translate all the potential parallelism of the control algorithm into the hardware architecture, FPGAs only take a fraction of the switching period to execute the control algorithm. Such behavior makes FPGA-based controller comparable to their analog counterparts [6].

FPGA-based controllers preserve the advantages of analog controllers, such as high bandwidth and almost no processing delay, without including their limitations: parameter drifting and poor level of integration. Furthermore, a closer look to Figure 1.1c shows that a lot of time is left unused in each sampling period, leaving the capabilities of FPGAs unexploited.

Therefore, the remaining processing time can be used to improve the performance of the controller by making use of *oversampling* techniques, *predictive* control and combine it with the possibility to redesign peripherals to a very precise level of detail.

Figure 1.1: Processing time distribution: (a) General-purpose microcontroller, (b) DSP, (c) FPGA.

# 1.2 Objectives

The objective of this work is to develop a control technique for power converters that takes advantage of the powerful processing capabilities of FPGAs, which also brings the possibility to modify conventional peripherals to a very precise level.

A novel predictive variable switching frequency modulator-based control scheme for the PMSM is to be developed and validated. The advantages of field-oriented control and model-based predictive control are to be combined to create a novel control strategy.

Furthermore, the fast sampling times and highly accuracy of the Sigma-Delta ADCs can be used to improve the signal identification process of sensorless techniques.

#### 1.3 State of the Art

A description regarding the state of the art of variable switching frequency modulator-based as well as model-based predictive control in the area of power electronics is presented. Because this project was implemented using an FPGA, a revision on state of the art regarding power electronic applications is also included.

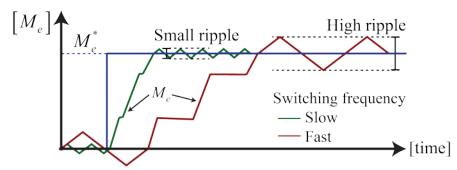

#### 1.3.1 Variable Switching Frequency

It is well known that commutation losses are directly related to the switching frequency of the power converter. A trade-off between the commutation losses and the introduced harmonic distortion (THD), or the dynamic performance of the control e.g. the settling time or the torque ripple among other criteria, is always hard to find. Conventionally, the switching frequency is usually fixed when the control technique works with a modulation stage, like in the field-oriented control (FOC) [7], or is of variable nature as in direct torque control (DTC) [8].

Random pulse-width modulation (RPWM) is a widely used implementation of variable switching frequency modulation that has many years of existence [9]. This method maintains the switching frequency constant; however, the acoustic noise is randomly spread over a wide spectrum making it more pleasing to the human ear. RPWM is in constant development [10], [11], later it has been used to reduce the harmonic distortion introduced by the modulation technique [12].

In the case of single-phase inverters, the choice of the switching frequency has to be adjusted between the THD and the switching losses. Based on a detailed time-domain analysis of the current distribution Mao X. et al [13] in 2009 propose a variable switching method to reduce the switching losses and regulate the current ripple. Experimental results are presented, consisting of the full-bridge inverter with an LC filter and a resistive load.

One of the more detailed works on variable switching frequency modulator-based is that of Jiang D. et al. [14] in 2013, where two algorithms are proposed to change the switching frequency based on a current ripple criterion. The current ripple is calculated for a given fixed switching period and then proportionally updated; one method is aimed

to control the maximum current ripple peak while the other regulates the RMS value. Experiments are carried out on a three-phase RLC load, successfully regulating the current ripple mainly in steady-state. Wang Z. et al propose a chaotic space phasor modulation technique to be used in conjunction with FOC and DTC schemes in [15], to reduce the harmonics introduced by fixed switching frequencies; experimental results are presented.

#### 1.3.2 Sensorless Control

Sensorless AC drives i.e. AC drives without angular encoder for the measurement of the angular position are much desired because of their advantages. By discarding the mechanical sensor, the hardware complexity can be reduced the noise immunity and reliability can be improved, along with fewer maintenance requirements [2]. Therefore, sensorless control schemes have been extensively researched in the past decades. These advanced control schemes have been enabled because of the constant increase in computational power of modern microelectronics [3].

There is a wide diversity of methods for different operating conditions as presented in [2] by Holtz. Roughly, these sensorless control methods can be classified in *fundamental wave* models and *signal injection* techniques. The *fundamental wave* models are based on the voltage model of the machine. Given that in voltage source inverter fed drives the stator voltage is a forced known quantity. Consequently, the estimate of the stator voltage can be integrated yielding the stator flux linkage, which can be used to obtain the stator field angle.

The main disadvantages of the *fundamental wave* models are DC-offset and drift effects derived from analog signal measurement, causing an accumulation of DC components at the integrator output. By introducing a negative low-gain feedback, the integrator can be stabilized. Another problem is the inaccuracies introduced by estimating the stator voltages, making the real and control values differ mainly because of the nonlinear dead-time delay. Finally, despite all the efforts to improve the performance of these models they become unobservable at zero frequency [2], [3].

The *signal injection* techniques make use of the anisotropic properties of the machine that are not included in the fundamental wave models. A test signal is used to excite the machine, it usually much higher that the fundamental frequency of the stator. These high-frequency signals do not affect the mutual flux linkage with the fundamental wave; therefore the high-frequency identification loop can be considered independent

of the fundamental wave control. As opposed to the fundamental wave models, these methods can be used at zero frequency.

In spite of all its disadvantages, the *fundamental wave* models are the most accepted ones in the industry. Perhaps first introduced by Frus and Kuo in 1976 in [16] since then, a great deal of progress has been achieved, like Barinberg et. al enhances the voltage model with an observer in [17]. Acarnley and Watson have a good review of the advancements in [18]. The most recent research on this topic has been done on the low-speed operation, some of the first works done by Jansson et al in [19] achieving a stable speed reversal, with work being continuously done [20]–[22].

In the case of the *signal injection* methods, Schroedl presented some of the first developments in [23], called the INFORM (indirect flux detection by online reactance measurement.) Some years later came to the alternating carrier injection by Linke and Kennel [24]. There is also some steady progress done on the research pertinent to these methods, most of them allowing a full range of the sensorless drive operation [25]–[27]. Perhaps some of the most recent and relevant research on this topic is being carried for medium voltage applications on the electrically excited synchronous machine (EESM) [22], [28], [29].

#### 1.3.3 Model-based Predictive Control

Since the introduction of FOC and DTC more than 30 years ago, these control techniques have become the standard for variable speed controlled drives; nonetheless, these methods have their limitations and disadvantages. Model-based Predictive Control (MPC) is the only one among many other advanced control techniques (techniques which are more advanced than standard PID control) that has been of great influence on the research and development directions of industrial control systems, with many successful practical applications [30].

Although Predictive Control has yield a wide range of different schemes, they all have a main characteristic: the use of the model of the system for the prediction of the feature behavior of the controlled variables. Model-based Predictive Control (MPC) also known as *receding horizon control* has slowly matured with decades of continuous development, some of the first ideas first ideas on MPC date back the 1960s [31], since then it has slowly matured with time mainly used in the process industry [32].

With the constant increase in digital signal processing capabilities of microprocessor units, its application was possible in the field of power electronics [33],

[34]. The idea of MPC comes from the deadbeat predictive control technique, in this approach a model of the controlled system is used to calculate the required voltage reference so that the reference value is reached in the next sampling instant; this process is done once every sampling period. The voltage is then applied using a pulse-width modulation technique.

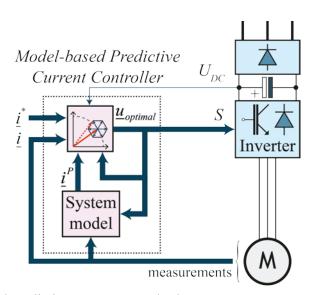

The main characteristic of MPC is the use of a model of the controlled system for the prediction of the possible future actions of the controlled variables; the controller uses this information in such a way that the optimal control action can be obtained, given an already established optimization criterion; which is expressed as a quality function to be minimized. MPC for power electronics has been mainly classified as Continuous Control Set (CS), which uses a modulator to generate the voltage outputs and Finite Control Set (FS) or Direct MPC, which considers only the natural space voltage phasors that the voltage source inverter can generate and thus, work without a modulator.

In CS-FCS, the optimization problem is analytically solved, the most developed method is the generalized predictive control (GPC), which has been proven to be fast enough for drive control [33]–[36]. Nevertheless, it becomes difficult to include system constraints in the algorithm. The switching frequency is usually fixed; the harmonic distortion introduced by the PWM is low. However, due to the long sampling times derived from low switching frequencies, the dynamic performance is usually worse than in linear controllers and the computational requirements are very high.

In [37] a multi-sampled method is proposed suitable for low switching frequencies, which solution is computed offline because of its heavy computational requirements. Another application of CS Nonlinear MPC aimed to control the flux and torque of an induction machine is presented in [38], it is implemented on a low-cost FPGA to demonstrate the feasibility of a cost-effective industrial drive system and tackle the high computational burden. Some of the newest contributions in the field of CS-MPC applied to power converters are presented in [39], [40].

The implementation of FS-MPC is much simpler and faster because the optimization solution does not have to be analytically found. The modulator stage can also be avoided, reducing the set of solutions to a finite set. Finally, if the prediction horizon is reduced to one, the optimization process becomes very trivial [30]. Nonetheless, to ensure a good performance, a high sampling rate is required, which also increases the computational effort. Moreover, because the switching frequency is variable, the harmonic distortion is hard to be determined and therefore controlled.

Another difficult task is to select a new voltage space phasor that will keep the desired torque and flux references while reducing the switching frequency.

Several applications of FS-MPC to power converters can be found in the literature [30], [41]–[47], all presenting better dynamic response than conventional PI-Control used in field-oriented control optimizations. Although most of the implementations are of variable switching frequency, in [44] it is shown that lower switching frequencies in conjunction with a modulation technique, can also deliver the high dynamic performance of conventional FS-MPC.

The possibility to include constraints on the cost function had made this type of MPC very popular in power electronics. The steady-state error remains an open issue for MPC [4], [48], to solve this problem the use of an integral term in the cost has been proposed in [49] and [50]. The calculation of the integral part is different to conventional linear PI-control because it has to be explicitly calculated along each sampling period based on a continuous model.

#### 1.3.4 FPGA-based Control Schemes for Power Electronics and Drives

Novel industrial control systems must have a high performance, along with high reliability and flexibility. At the same time, the cost is also an important issue, time-to-market hast to be reduced as much as possible, the price of the controller has to be as low as possible as well as its energy consumption and of the controlled system. On top of that, the cost reduction gets even more challenging because the complexity of sophisticated control algorithms demands a lot of computing resources and reduced execution times [5].

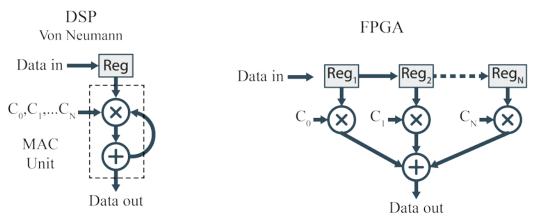

Traditionally, there are two different approaches that designers can follow to implement digital control systems for industrial applications. The first is the pure software platform, associated to microcontroller or Digital Signal Processor controllers (DSP) [51]. These devices integrate a microcontroller unit along with several peripherals necessary to control the targeted system in real-time and communicate with external devices. The difference between microcontroller and DSP is the ratio between processing power and integrated peripherals. While the microcontroller integrates a general processing unit with many control and communications devices, the DSP integrate a high-performance processor unit and few peripherals.

Nevertheless, the boundaries between these two concepts are fading because microcontrollers are becoming more and more powerful while DSPs get more peripherals integrated. The main advantages of this approach are the reliability of these technologies and their reduced costs; whereas the main drawback is the performance limitation due to the sequential execution related to software platforms, thus the potential parallelism that control algorithms can achieve remains unexploited.

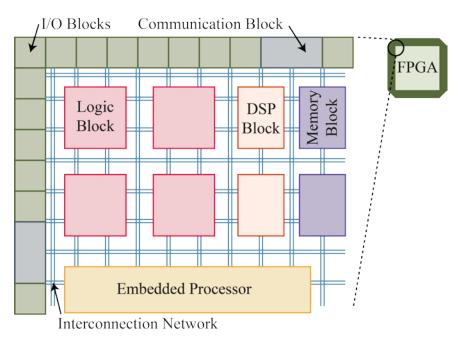

The alternative approach is the use of Field Programmable Gate Arrays (FPGAs), which are devices that consist of elementary cells and interconnections that are fully programmable by the end user, enabling them to build specific hardware architectures that match the desired application. FPGAs can be seen as programmable microcontrollers with dedicated peripherals and hardware accelerators that allow the implementation of parallel algorithms.

FPGAs were originally used to integrate logic circuits usually designed with TTL basic logic circuits; on which simple Computer-Aided Design (CAD) tools were used to develop these applications. These days, FPGAs are being used to implement more and more complex tasks. This progress can be attributed to the steady evolution of tools that were originally reserved to ASICs; these tools are mainly based on Hardware Description Languages (HDLs), being VHDL and Verilog the most prominently used.

HDLs are mainly used to describe hardware and are essentially used to describe concurrent tasks i.e. actions that occur at the time; this is a great difference when compared to high-level computer languages, which are used to describe algorithms that are sequentially executed. However, a common mistake made by someone new to HDLs is to attempt to program them as high-level software languages [52].

The existence of IEEE Standards for these HDLs [53]–[55] has allowed the creation of high-performance CAD tools in the field microelectronics [6]. Conventionally, the designers take advantage of these tools to build digital circuits following a hierarchical and modular approach, in which ideas are defined at different levels of abstraction. Then the design has to be simulated by creating test-benches and later validate it with synthesized HDL code.

However, the design of FPGA-based controllers is rather intuitive and require that the designer master several areas e.g. microelectronics, control, electrical machine theory. All of these skill requirements naturally ends leading many control engineers to choose standard, already proved platforms, such as DSPs [56]. In the recent years, a plethora of methodologies to reduce the complexity of the design approach [6], [57]—

[59] have been proposed. All of them are based on friendly development procedures considering that the control engineer is not proficient in microelectronics.

Moreover, FPGA vendors are redesigning their development tools work with high-level programming languages such as C/C++ and more recently OpenCL [60], [61], allowing the designers to describe hardware components using these high-level languages. The latest generations of FPGAs integrate powerful embedded processor units making them full system-on-chip (SoC) platforms; thus, their applications are no longer reduced to hardware acceleration. To take full advantage of these SoC solutions, the use of software/hardware co-design methodologies is crucial [58].

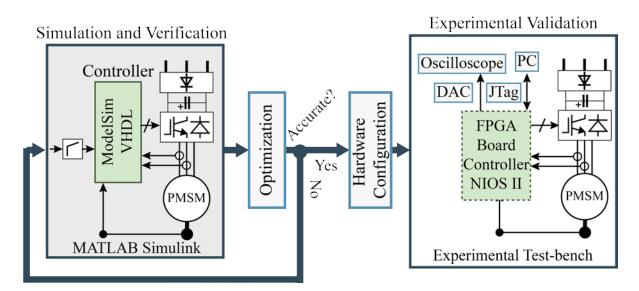

A recent popular approach is Model-Based Design (MBD) for FPGAs, which allows the designers to simulate and later translate their design within MATLAB-Simulink friendly environments. The results of these simulations are later accurately translated to the hardware implementation, allowing rapid prototyping schemes [62]. Nevertheless, in the case of complex algorithms, this solution still leads most of the time, to un-optimized architectures regarding consumed resources [6], [56].

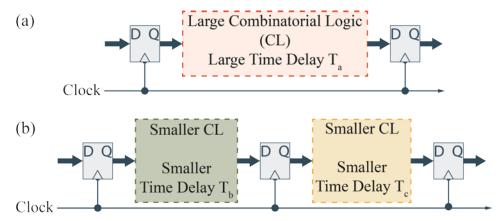

In all the cases, the most restraining factor for the control of a power converter is the constraining of the switching frequency due to the commutation losses. Based on this idea, two groups can be identified: high demanding applications and constrained switching frequency applications [5]. In the first case, the timing constraints are so rigorous that the digital controller represents the main limitation of the whole control loop [63]. One example of this type of application, are power converters based on wide bandgap semiconductors devices like Silicon Carbide (SiC) and Gallium Nitrate (GaN) that are allowing power converters work at several hundreds of kilohertz and even the megahertz switching frequencies [64]–[67].

On the second case where the switching frequency is constrained, using FPGA is of great interest because the control processing time can be drastically reduced, up to a fraction of the sampling period. Thus the behavior of the digital controller is very close to its analog counterpart [68], [69]. With the extra remaining time, enhancing capabilities can be added to the control algorithm, such as predictive schemes [70] and control of very complex systems [70], [71], real-time fault detection [72], among many others.

# 1.4 Outline of the Chapters

The structure of this work is organized as follows: Chapter 1 contains the motivations, objectives, and a brief review of the state of the art of the theories and technologies in which this work lays on. Chapter 2 summarize the theoretical fundamentals used for the development of this work like the space phasor theory, the modelling of the PMSM, field-oriented control, and model-based predictive control among others.

Following, the chapter 3 describes the fundamentals of FPGAs and the necessary concepts to understand the analog-to-digital conversion process made by sigma-delta converters. In chapter 4 the concepts and ideas around the proposed predictive variable switching frequency control are presented. Finally, in chapter 5 experimental results used to validate the proposed control are presented and discussed and chapter 6 the conclusions of this work are discussed as well as the relevance of the obtained results.

## 2 Theoretical Fundamentals

Electrical machine users are interested in the way their mechanical quantities (torque, speed, power) behave but in order to understand them, the electrical quantities (currents, voltages) have to be described and as a result, the complete behavior of the machine can be studied. Therefore, this chapter presents some fundamental concepts that were used for the development of this work.

# 2.1 The Space Phasor

There are many methods to describe electrical machines for instance, the matrix calculation, which yields to a more difficult and less clear mathematical description. The space phasor is a simple and powerful method; additionally, it allows the final user to see the physical background of various phenomena [73]. Kovacs and Racz [74] introduced the space phasor theory in 1959, it was further developed by Stepina J. [75] and Serrano-Iribanegaray [76]–[78]. The study of electrical machines require the knowledge of these internal and external quantities, which are spatially distributed and space phasors happen to be very appropriate to describe them [78]. In general, the instantaneous values of the three-phase quantity r can be described in the complex space phasor  $\underline{r}(t)$  form as follows:

$$\underline{r}(t) = \frac{2}{3} \left( r_U(t) + \underline{a} \cdot r_V(t) + \underline{a}^2 \cdot r_W(t) \right) \cdot e^{j\gamma_i}$$

(2.1)

$$\underline{a} = e^{j\frac{2\pi}{3}} = -\frac{1}{2} + j\frac{\sqrt{3}}{2} \tag{2.2}$$

where:  $r_U(t)$ ,  $r_V(t)$  and  $r_W(t)$  are the electric or magnetic instantaneous values of a three-phase system of the respective U, V and W phases and the spatial operator is given by (2.2). For stator quantities the angle  $\gamma_i = \gamma_1$  and for rotor quantities  $\gamma_i = \gamma_2$ . Consequently, the stator current space phasor can be defined as:

$$\underline{i}_{1} = \frac{2}{3} \left( i_{U} \left( t \right) + \underline{a} \cdot i_{V} \left( t \right) + \underline{a}^{2} \cdot i_{W} \left( t \right) \right) \cdot e^{j\gamma_{1}}$$

$$(2.3)$$

The angle  $\gamma_1$  defines the position of the axis to the first stator winding U with respect an arbitrarily defined reference frame; which is often selected as  $\gamma_1 = 0$ . The 2/3 factor in (2.3), scales the length of the space phasor to the correspondent amplitude of the phase current in a symmetric sinusoidal system. Usually the windings of a three-phase alternating current machine are either connected in delta or star with isolated neutral point:

$$i_U + i_V + i_W = 0 (2.4)$$

Therefore, it is possible to calculate the instantaneous values of the phase currents from the space phasor and the other way around, without losing information. Space phasors can also be represented in different coordinate systems; in the following, the required systems for this work will be described.

#### 2.1.1 Fixed α,β-Coordinate System

The space phasor is a complex function with real and imaginary time-dependent parts and is referred to a given complex plane, whose orientation in space has to be defined. As previously mentioned, one of the most used coordinates systems is defined by pointing the real axis of the space phasor in the direction of the first stator winding, usually called U.

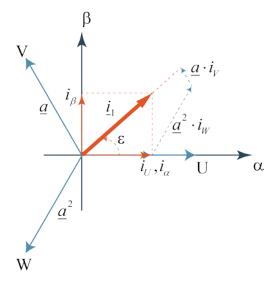

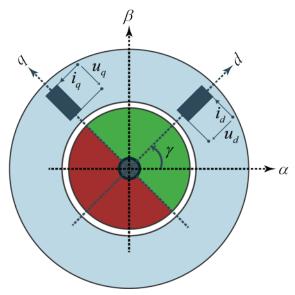

Figure 2.1: Graphical representation of the current space phasor in the stator fixed coordinate system.

This system, depicted in Figure 2.1 is known as stator-fixed coordinate system, the real and imaginary axes are named as  $\alpha$ - and  $\beta$ -axis respectively:

$$\underline{i}_{1} = \frac{2}{3} \left( i_{U}(t) + \underline{a} \cdot i_{V}(t) + \underline{a}^{2} \cdot i_{W}(t) \right) \cdot e^{j\gamma_{1}} = i_{1\alpha} + j \cdot i_{1\beta} = i_{1}(t) \cdot e^{j\varepsilon(t)}; \text{ with } \gamma_{1} = 0 \quad (2.5)$$

$$i_{1\alpha} = \text{Re}\left\{\underline{i}_1\right\} \tag{2.6}$$

$$i_{1\beta} = \operatorname{Im}\left\{\underline{i}_{1}\right\} \tag{2.7}$$

From (2.4) it is known that the sum of the phase values is zero, therefore it is possible to obtain the current components along the real and imaginary axes as:

$$i_{1\alpha} = i_{U} \tag{2.8}$$

$$i_{1\beta} = \frac{1}{\sqrt{3}} (i_V - i_W) \tag{2.9}$$

Similarly, the instantaneous values of the phase quantities related to the stator current space phasor can be obtained from the spatial projection of  $\underline{i}_1$  on the three-phase axes:

$$i_{1U} = \operatorname{Re}\left\{\underline{i}_{1}\right\} = i_{1\alpha} \tag{2.10}$$

$$i_{1V} = \operatorname{Re}\left\{\underline{i}_{1} \cdot \underline{a}^{-1}\right\} = -\frac{1}{2} \cdot i_{1\alpha} + \frac{\sqrt{3}}{2} \cdot i_{1\beta}$$

(2.11)

$$i_{1W} = \operatorname{Re}\left\{\underline{i}_{1} \cdot \underline{a}^{-2}\right\} = -\frac{1}{2} \cdot i_{1\alpha} - \frac{\sqrt{3}}{2} \cdot i_{1\beta}$$

(2.12)

$i_{1\alpha}$  and  $i_{1\beta}$  can be seen as the instantaneous currents in a similar two orthogonal phase windings that create the same resultant mmf-wave as the three-phase windings; from this perspective equations (2.10) to (2.12) denotes a three-phase to two-phase variable transformation, being the  $\alpha$ -phase on the equivalent two-phase machine coincident with the U-phase of the three-phase machine. From this point on, the indices  $\alpha$  and  $\beta$  will be used to design stator-related quantities based on the stator-fixed reference frame. Equations (2.5) to (2.12) are also valid for other electrical or magnetic quantities such as: voltage  $\underline{u}$ , flux linkages  $\underline{\psi}$ , magnetic flux density  $\underline{B}$ , many others.

#### 2.1.2 Rotating *d,q*-Coordinate System

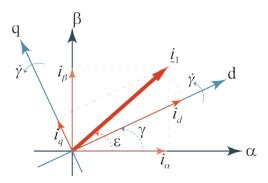

The rotating d,q-coordinate system becomes its name from the *direct* and *quadrature* axes. As shown in Figure 2.2, the current space phasor (2.3) referred to the stator-fixed  $\alpha,\beta$ -coordinate system, can be transformed into a rotating d,q-coordinate system, where  $\gamma$  is the angle between the real  $\alpha$ -axis of the fixed reference frame and the real d-axis of the rotating reference frame, which can vary in time as  $\gamma(t)$ .

In the case of the PMSM, which is used for the development of this work, the rotating d,q-coordinate system is aligned to permanent rotor flux. Considering the rotation of the system, the relations on equations (2.13) and (2.14), so that the rotation from the  $\alpha,\beta$ - to the d,q-reference frames can be performed with (2.15) and inversely with (2.16).

$$i_{1\alpha} + j \cdot i_{1\beta} = \underline{i}_1 \cdot e^{j\varepsilon} \tag{2.13}$$

$$i_{1d} + j \cdot i_{1q} = \underline{i}_1 \cdot e^{j(\varepsilon - \gamma)}$$

(2.14)

$$\left(i_{1\alpha} + j \cdot i_{1\beta}\right) = \left(i_{1d} + j \cdot i_{1q}\right) \cdot e^{j\gamma} \tag{2.15}$$

$$\left(i_{1d} + j \cdot i_{1q}\right) = \left(i_{1\alpha} + j \cdot i_{1\beta}\right) \cdot e^{-j\gamma}$$

(2.16)

From now on, the indices d and q will be used to name stator-related quantities based on the rotational reference frame.

Figure 2.2 :Transformation of fixed  $\alpha,\beta$ -coordinate system to the rotating d,q-coordinate system.

#### 2.1.3 Coordinate Transformations

With the introduction of the current space phasor and the different reference systems, some transformations can be derived. As presented in Figure 2.1 and from

equations (2.5), (2.8) and (2.9) the transformation of a three-phase system to an orthogonal two-phase coordinate system can be described by the following expression:

$$\begin{bmatrix} r_{\alpha} \\ r_{\beta} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 2 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 \\ 0 & \frac{\sqrt{3}}{3} & -\frac{\sqrt{3}}{3} \end{bmatrix} \cdot \begin{bmatrix} r_{U} \\ r_{V} \\ r_{W} \end{bmatrix}$$

(2.17)

Conversely, the inverse transformation can be derived from equations (2.10) - (2.12), as:

$$\begin{bmatrix} r_U \\ r_V \\ r_W \end{bmatrix} = \begin{bmatrix} 1 & 0 \\ -\frac{1}{2} & \frac{\sqrt{3}}{2} \\ -\frac{1}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \cdot \begin{bmatrix} r_\alpha \\ r_\beta \end{bmatrix}$$

(2.18)

The transformations for the fixed to rational reference frames can be also derived, if the real and imaginary terms from (2.15) and (2.16) are compared the following matrix expressions are obtained:

$$\begin{bmatrix} r_d \\ r_q \end{bmatrix} = \begin{bmatrix} \cos \gamma & \sin \gamma \\ -\sin \gamma & \cos \gamma \end{bmatrix} \cdot \begin{bmatrix} r_\alpha \\ r_\beta \end{bmatrix}$$

(2.19)

Being the inverse transformation:

$$\begin{bmatrix} r_{\alpha} \\ r_{\beta} \end{bmatrix} = \begin{bmatrix} \cos \gamma & -\sin \gamma \\ \sin \gamma & \cos \gamma \end{bmatrix} \cdot \begin{bmatrix} r_{d} \\ r_{q} \end{bmatrix}$$

(2.20)

These coordinate transformations are also known as vector-rotations.

# 2.2 Permanent Magnets Synchronous Machine

The first permanent magnet (PM) excitation systems applied to electrical machines date back to the 19<sup>th</sup> century, however, the use of very poor magnetic materials discouraged their use, in favor of electromagnetic excitation systems. The discovery of the AlNiCo (an alloy of iron with aluminum, nickel, and cobalt) magnet in 1932 brought back to attention the PM excitation system. Nevertheless, at that time the performance

of the magnetic material was not enough and the development of power electronics was yet to come, so the applications of PMSM where limited [79].

The Permanent Magnets Synchronous Machine (PMSM) has gained a lot of interest over the years; mainly due to several advantages including high power density, high efficiency, and high reliability. They have a wide range of applications: like small disk drive units, high-performance motors for hybrid electric vehicles, to some megawatts machines used for oil and gas applications as well as wind turbines, and electric ship propulsion [79]–[81].

Like every rotating electrical machine, the PMSM is an energy converter as it can operate either as a generator or as a motor; it is composed of two parts: the stator and the rotor [82]. The stator is comprised of three identical windings symmetrically distributed in space (120° electric degrees between them). When the stator windings are current fed by a balanced three-phase alternating current (AC), a revolving field is generated along the air gap.

The rotation speed of the revolving field is proportional to the number of poles of the machine and the frequency of the stator currents. The rotor consists of permanent magnets, which replace the conventional electromagnetic field poles, thus eliminating the extra hardware like slip rings and brushes needed to excite the field windings [83]. For the development of this work a PMSM was considered, the construction and mathematical description will be further described in the following sections.

# 2.2.1 Permanent Magnets for Electrical Machines

During the decade of the 1950's materials that retain magnetism were introduced in electrical machine research. Materials that retain magnetism are known as *hard materials*. The ability to retain permanent magnetism is present in cobalt, iron, and nickel; which are also known as ferromagnetic materials. Several materials such as *AlNiCo*, ferrites (ceramic) such as barium ( $BaO6Fe_2O_3$ ) and strontium ( $SrP6Fe_2O_3$ ) ferrites, and rare-earth materials such as samarium-cobalt (SmCo) and neodymium-iron-boron (NdFeB) are available as permanent magnets for use in electrical machines [79], [83], [84].

Of these materials, *AlNiCo* has a high remanence flux yet small coercive field strength and can be quickly demagnetized. Therefore, this material is used since the end of the 1970's and has substituted the ferrite materials. The advantage of the ferrite

materials is their cost, as well as a large electrical resistance value, which reduces the development of Eddy-currents. Ferrite materials are mostly used in DC-actuators, the automobile industry and in fan motors.

Nevertheless, this material generates low torque density motors. *SmCo* has better magnetic characteristics; therefore machines with this material are smaller. Rotors with *SmCo* materials were used many years ago; they were later replaced by *NdFeB* magnets which are lower in cost but are sensitive to the temperature and prone to corrosion [49], [79], [85].

#### 2.2.2 Permanent Magnets Rotor Types

The permanent magnets of the PMSM can be classified by the direction of the field flux. In a *radial field* PM the flux directions flows along the radius of the machine, this is the most prominent configuration. In an *axial field* PM, the direction of the flux is parallel to the rotor shaft, these machines are getting more use because of their high power density and maximum possible acceleration capabilities [83].

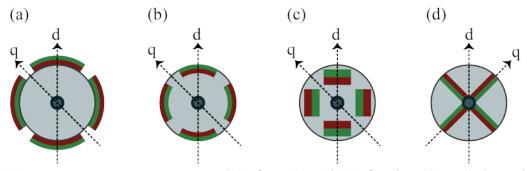

The magnets can be placed in many forms on the rotor; regardless of the way the permanent magnets are mounted the principle of operation of the machine is the same. However, it will impact on the values of the direct and quadrature axes inductances. In general, the permanent magnet rotors can be classified as *surface* and *interior* mounted, some examples can be found in Figure 2.3.

Figure 2.3: Permanent magnets rotor types: a) Surface. (SPM) b) Surface-inset (SIPM). c) Interior with radial orientation (IPM). d) Interior with circumferential orientation. All these rotors have two pairs of poles.

#### 2.2.2.1 Surface mounted permanent magnets

This arrangement (shown in Figure 2.3a) provides the highest air-gap flux density as the air-gap is directly without the intermission of any other part of the rotor. Because of this, the structural integrity is not so robust and therefore this kind of machines is normally not driven faster than 3000 min<sup>-1</sup>. The reluctance between the d,q-axes is fairly

small, (less than 10%) which allows the simplification of the model for this kind of machines.

#### 2.2.2.2 Interior permanent magnets

This kind of rotors can be further subdivided, depending on how deep are the permanent magnets buried in the rotor laminations. The interior-inset variant (as in Figure 2.3b) has the permanent magnets placed in the grooves of the outer periphery of the rotor laminations, providing a uniformly cylindrical surface on the rotor; this arrangement is much more mechanically robust than the surface mounted variant, which is usually called inset rotor.

Finally as shown in Figure 2.3c-d, the permanent magnets are placed in the middle of the rotor, they are called interior PMSM. This type of machines is the most mechanically robust and therefore suitable for high-speed applications. Their construction process is much more complex and the ratio between the direct and quadrature inductances is also the largest.

#### 2.2.3 Modeling of the PMSM

The behavior of the PMSM can be derived from the equations that describe the electrically excited synchronous machine (EESM). However, in the former, the excitation is provided by PMs on the rotor as opposed to the later, where a winding has to be excited with a DC current and a damping cage also part of the system making the mathematical model to be more complex. With the introduction of the space phasor, the current, voltage and flux phasor of the machine can be defined.

Therefore, the equations of the PMSM mathematical model can be derived from the EESM in the d,q-reference frame [22], [49], [85], by assuming that there is no damping cage and the permanent flux in the d-axis of the rotor is constant  $\psi_{d0}$ . The simplified structure of the windings is shown in Figure 2.4 for a two-pole model. In addition, the machine is considered to be magnetically symmetric, thus  $L_d = L_q = L_1$ :

$$\psi_d = L_1 \cdot i_d + \psi_{d0} \tag{2.21}$$

$$\psi_q = L_1 \cdot i_q \tag{2.22}$$

$$u_d = i_d \cdot R_1 + \frac{d\psi_d}{dt} - \omega \psi_q \tag{2.23}$$

$$u_q = i_q \cdot R_1 + \frac{d\psi_q}{dt} + \omega \psi_d \tag{2.24}$$

By replacing the flux equations in the voltage equations of the PMSM follows:

$$u_d = i_d \cdot R_1 + L_1 \cdot \frac{di_d}{dt} - \omega \cdot L_1 \cdot i_q$$

(2.25)

$$u_q = i_q \cdot R_1 + L_1 \cdot \frac{di_q}{dt} - \omega \cdot L_1 \cdot i_d + \omega \cdot \psi_{d0}$$

(2.26)

Figure 2.4: Model of a PMSM with two poles.

In addition to the electrical and magnetic equations, some mechanical quantities have to be mathematically described i.e. the rotor position and the angular speed are described so the system can be fully described. As presented in Figure 2.4, the angle between the  $\alpha$ -axis and the d-axis is denoted by  $\gamma$ , (this coordinate transformation is explained in 2.1.3). For a machine with p-pair of poles, the mechanical angle is defined by:

$$\gamma = p \cdot \gamma_{mech} \tag{2.27}$$

The electrical and mechanical angular velocities are described by:

$$\frac{d\gamma}{dt} = \dot{\gamma} = \omega \tag{2.28}$$

$$\frac{d\gamma_{mech}}{dt} = \dot{\gamma}_{mech} = \omega_{mech} \tag{2.29}$$

$$\dot{\gamma}_{mech} = \frac{\dot{\gamma}}{p} \text{ respectively } \omega_{mech} = \frac{\omega}{p}$$

(2.30)

The electromagnetic torque can be expressed as in (2.31) [73], which in d,q-components is described as in (2.32):

$$M_e = \frac{3p}{2} \cdot \operatorname{Im} \left\{ \underline{\psi}_1^* \cdot \underline{i}_1 \right\} \tag{2.31}$$

$$M_e = \frac{3p}{2} \cdot \operatorname{Im} \left\{ \psi_d \cdot i_q - \psi_q \cdot i_d \right\}$$

(2.32)

If the flux equations are introduced in the electromagnetic  $(M_e)$  torque equation  $\psi_{d0}$  is considered to be constant then  $M_e$  is proportional to  $i_q$ :

$$M_{e} = \frac{3p}{2} \cdot \left( L_{1} \cdot i_{d} \cdot i_{q} + \psi_{d0} \cdot i_{q} - L_{1} \cdot i_{d} \cdot i_{q} \right) = \frac{3p}{2} \cdot \psi_{d0} \cdot i_{q}$$

(2.33)

The mechanical equation (2.33) completes the mathematical modeling of the PMSM; where  $M_L$  defines the load torque and J the total moment of inertia of the driven masses as reflected to the shaft of the motor:

$$M_e - M_L = J \cdot \frac{d\omega_{mech}}{dt} = J \cdot \ddot{\gamma}_{mech} \tag{2.34}$$

# 2.3 Voltage Source Inverter

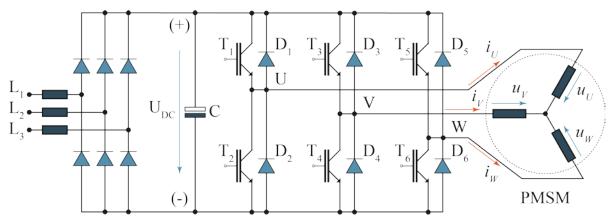

A power converter in its most simple expression is an array of on-off power electronic semiconductor switches that is able to convert and control electrical power. Of course, power converters are not ideal and these devices will introduce nonlinearities i.e. harmonics and electromagnetic interference (EMI) problems. A DC-to-AC power converter is known as an *inverter*. Thus, the function of an inverter is to convert a DC input voltage to a symmetric AC output voltage with a desired magnitude and frequency. If an inverter has a constant input voltage it is called Voltage Source Inverter (VSI) [86], [87].

The basic configuration of the power converter used to feed the PMSM is presented in Figure 2.5; it comprises a three-phase diode rectifier, a capacitive filter in DC-link and a three-phase VSI. The inverter is made of six Insulated Gate Bipolar Transistors

(IGBTs)  $(T_1 - T_6)$  and six free-wheeling diodes  $(D_1 - D_6)$ . With this kind of VSI topology, it is possible to get eight different states of the switches in the inverter i.e. eight different space voltage phasors.

Figure 2.5: Three-phase power converter connected to the stator of the PMSM.

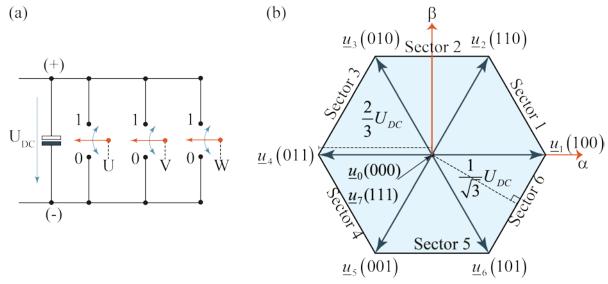

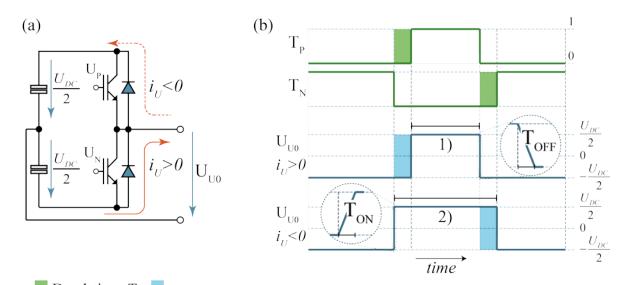

## 2.3.1 Generation of the Voltage Space Phasors

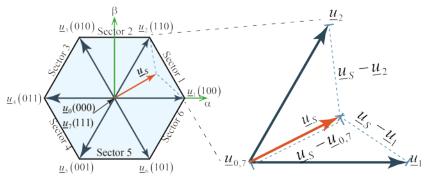

The switches on the VSI are defined as  $(S_U, S_V, S_W)$  where the value "1" defines the switch set to the positive voltage and "0" when the switch is set to the negative voltage (the simplified diagram can be seen in Figure 2.6a; the eight different switching configurations generate a the voltage space phasors:  $\underline{u}_0, \underline{u}_1, \underline{u}_2, \underline{u}_3, \underline{u}_4, \underline{u}_5, \underline{u}_6, \underline{u}_7$ . The two space phasors  $\underline{u}_0, \underline{u}_7$  are the zero voltage space phasors (ZV) with the all the phases connected to the negative potential or all connected to the positive potential, respectively; the rest  $\underline{u}_1 \dots \underline{u}_6$  are called active voltage space phasors (AV), as can be seen in Figure 2.6b.

Figure 2.6: a) Simplified switching scheme of a two-level VSI. b) Voltage space phasors derived from the switching states of a two-level VSI.

The voltage space phasors divide the plane into six sectors every  $60^{\circ}$  or  $\pi/3$  radians, as presented in Figure 2.6b, which can be mathematically described as in equation (2.35). Finally, the components in the  $\alpha,\beta$ -reference frame of the eight available space voltage phasors are presented in Table 2.1.

$$\underline{u}_{1} = \underline{u}_{\nu} = \begin{cases} \frac{2}{3} \cdot U_{DC} \cdot e^{j(\nu - 1)\frac{\pi}{3}} & \nu = 1, \dots 6 \\ 0 & \nu = 0, 7 \end{cases}$$

(2.35)

| Voltage space phasor                             | $\underline{u}_0$ | $u_1$         | $u_2$    | $u_3$          | $u_{4}$        | $\underline{u}_5$ | $u_6$          | $u_7$ |

|--------------------------------------------------|-------------------|---------------|----------|----------------|----------------|-------------------|----------------|-------|

| Switching state                                  | 000               | 100           | 110      | 010            | 011            | 001               | 101            | 111   |

| $\underline{u}_{\alpha}$                         | 000               | 2             | 110      | 1              | 2              | 1                 | 2              | 111   |

| $\frac{\underline{\underline{\omega}}a}{U_{DC}}$ | 0                 | $\frac{2}{3}$ | 1 2      | $-\frac{1}{2}$ | $-\frac{2}{3}$ | $-\frac{1}{2}$    | $\frac{2}{3}$  | 0     |

|                                                  |                   | 3             | <u> </u> | <u>3</u><br>1  | 3              | <u> </u>          | <u> </u>       |       |

| $\frac{\underline{u}_{eta}}{U_{DC}}$             | 0                 | 0             | <u></u>  | <u></u>        | 0              | - <del>1</del>    | - <del>1</del> | 0     |

Table 2.1: Voltage space phasors in the  $\alpha,\beta$ -reference frame

# 2.4 Space Phasor Modulation

This technique arises from the idea that inverters are only capable of generating a finite number of voltage space phasors, as presented in section 2.3, the two-level VSI is capable of generating eight. Nevertheless, if the stator voltage space phasor to be applied differs from the natural voltage space phasors that the inverter can generate, then different combinations of the available voltage space phasors have to be applied in order to create the desired output; this process is also known as modulation.

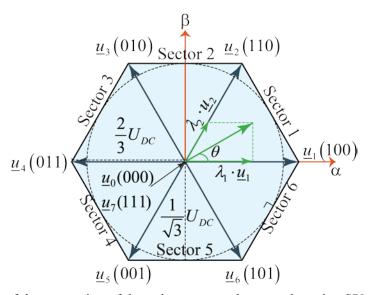

Figure 2.7: Example of the generation of the voltage space phasor  $u_s$  by using SPM.

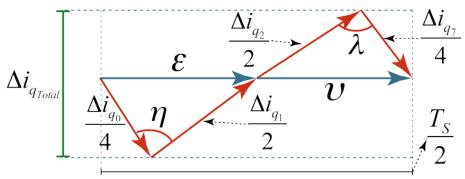

One of the most well-known modulation techniques is the space phasor modulation (SPM) [88] technique (also referred as space vector modulation SVM), which relies on the space phasor theory. The SPM technique generates the voltage space phasor  $\underline{u}_S$ , which can be located inside one of the sectors of the hexagon voltage-limits of the VSI (Figure 2.6b), using the three nearest voltage space phasors (two active and one zero voltage space phasors).

Figure 2.7 shows as an example the voltage space phasor  $\underline{u}_S$  located in the first sector, in order to create the desired voltage space phasor. During one modulation period the active voltage space phasors  $\underline{u}_1$  and  $\underline{u}_2$  should be applied the respective  $\lambda_1$  and  $\lambda_2$  intervals of time, in which the space phasors are active, as well as the zero voltage space phasors  $\underline{u}_0$  and  $\underline{u}_7$  for the rest of the modulation period.

$\lambda_1$  and  $\lambda_2$  are the duty cycles of the active space phasors and correspond to the length of the projections of the desired space phasors on the direction of the active space phasors. Thus, the voltage space phasor  $\underline{u}_S$  can be calculated by the following expressions:

$$\underline{u}_S = u_S \cdot e^{j\theta} = \lambda_1 \cdot \underline{u}_1 + \lambda_2 \cdot \underline{u}_2 \tag{2.36}$$

$$\lambda_k = \frac{T_k}{T_S} \quad k = 0..7 \tag{2.37}$$

Where  $T_S$  is the duration of one modulation period and  $\lambda_k$  is the power-on time within one  $T_S$  or the duty cycle of the respective voltage space phasor i.e. switching cycle i. The active duty-cycles  $\lambda_k$  for the first sector can be calculated as follows:

$$\lambda_{1} = \frac{T_{1}}{T_{S}} = \frac{2}{\sqrt{3}} \cdot \frac{u_{S}}{u_{\text{max}}} \cdot \sin\left(\frac{\pi}{3} - \theta\right)$$

(2.38)

$$\lambda_2 = \frac{T_2}{T_S} = \frac{2}{\sqrt{3}} \cdot \frac{u_S}{u_{\text{max}}} \cdot \sin(\theta)$$

(2.39)

$$\lambda_{0,7} = 1 - \lambda_1 - \lambda_2 \tag{2.40}$$

Where:  $0 \le \theta \le \pi/3$ .

During the rest of the modulation period  $T_{0,7} = \lambda_{0,7} \cdot T_S$  one of the two zero space phasors  $\underline{u}_0$  and  $\underline{u}_7$  is applied. From Figure 2.7 it can be seen that the maximum amplitude

of the voltage space phasors is  $u_{max} = 2U_{DC}/3$ ; nonetheless, for some practical cases e.g. reduction of harmonics in the output voltage, only the inner circle in the hexagon limit is used which corresponds to  $u_{max} = U_{DC}/\sqrt{3}$  [89]. Following this, the sequence in which the voltage space phasors are applied has to be determined.

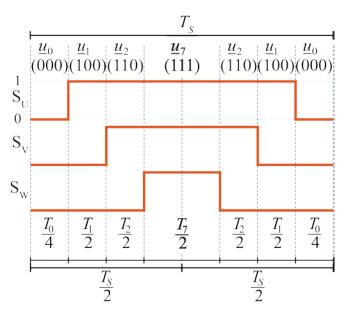

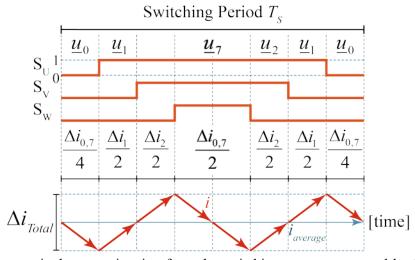

From the switching losses point of view, it can be noticed that the most favorable sequence is to change the state of every pair of switches only once every switching period. Figure 2.8 presents the switching patterns of the voltage space phasors in the first sector, a conventional implementation of SPM applies a zero space phasor at the beginning and end of the switching period. This will reduce the current ripple, reducing the torque ripple and magnetic losses associated with ripple currents in the machine [83]. In this figure, it can also be noted that the switching period is the double of the modulation period  $T_S$ , a similar procedure can be followed for the remaining sectors.

Figure 2.8: Switching patterns of the voltage space phasors in the first sector.

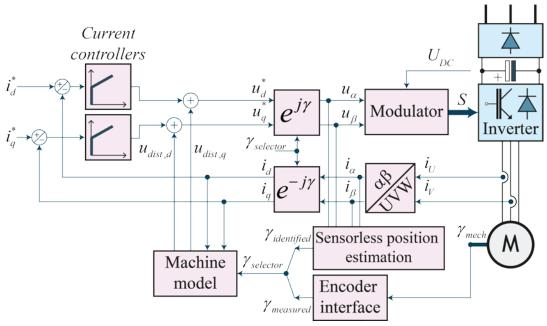

# 2.5 Field Oriented Control Principle

Field Oriented Control (FOC) was developed and first presented by Hasse and Blaschke [7], [90], [91], the idea behind this control technique is inspired by the DC control schemes, where the flux and torque are decoupled and therefore the mathematical modeling is simplified. Thus, by orienting or aligning the reference frame to a rotating  $d_{,q}$ -coordinate system, the decoupling of the flux and torque forming components of the variables in the AC machine is achieved (see Figure 2.9) [89].

Figure 2.9: Fundamental blocks of the field-oriented control scheme.

If the equation for the  $i_d$  and  $i_q$  currents were absolutely decoupled, like in the case of the DC machine for the armature and field current, this idea would perfectly work with two separate PI current controllers. However if the voltage equations of the machine are carefully analyzed, in particular for the PMSM presented in (2.25) and (2.26), it can be noticed that a coupling between these equations exists. The stator voltage in each axis is coupled through the rotational voltage of its orthogonal axis, which can be better understood if the equations are rewritten as follows:

$$u_d = i_d \cdot R_1 + L_1 \cdot \frac{di_d}{dt} - \omega \cdot L_1 \cdot i_q = i_d \cdot R_1 + L_1 \cdot \frac{di_d}{dt} + u_q^{dist}$$

(2.41)

$$u_{q} = i_{q} \cdot R_{1} + L_{1} \cdot \frac{di_{q}}{dt} - \omega \cdot L_{1} \cdot i_{d} + \omega \cdot \psi_{d0} = i_{q} \cdot R_{1} + L_{1} \cdot \frac{di_{q}}{dt} + u_{d}^{dist}$$

$$(2.42)$$

Therefore, these  $u_d^{dist}$  and  $u_q^{dist}$  can be considered as disturbances quantities by the controllers, which are calculated using a model of the machine and added to the output of the current controllers. The reference voltages  $u_d^*$  and  $u_q^*$  are then transformed to the stator-fixed  $\alpha,\beta$ -reference frame, which are in turn used by the modulator to generate the desired switching signals for the inverter. The modulator implements the SPM technique presented in 2.4 or some other kind of pulse-width modulation technique.

The reference  $i_q^*$  can be obtained from a super-imposed speed controller or a direct desired torque reference. The  $i_q^*$  reference value is generally set to zero for the PMSM

therefore no additional flux controller is needed; a different situation could arise if the machine shall operate in the field-weakening region. In order to achieve this, a negative current should be fed in the *d*-axis, depending on the desired speed; mainly because the modern PM are nearly impossible to be demagnetized [89].

It can be concluded that a good dynamic performance of the current controllers will derive in a good dynamic response of the electromagnetic torque as well as the magnetic flux being kept around the desired reference value.

## 2.6 Model-based Predictive Control Principle

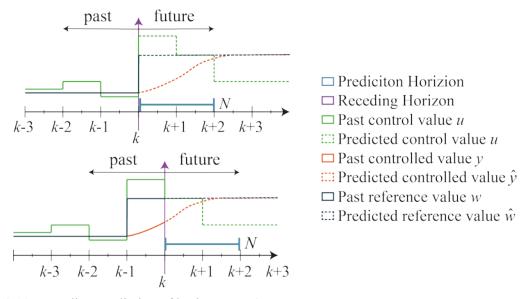

A wide range of predictive control methods have found applications in power electronics. All these methods share a same idea, the use of a model of the controlled system for the prediction of the future actions of the controlled variables. With this information and a predefined optimization criterion, the controller will choose the optimal action, in the case of model-based predictive control (MPC) the optimization criterions is expressed as a cost function to be minimized [30].

For power electronics the variations of MPC are classified depending on the use of a modulation stage or not. In the first case, a continuous set of solutions (CS-MPC) [35] resulting in a fixed switching frequency. The second case, generates the switching signals for the power converter directly coming from the natural voltage space phasors that the inverter is able to generate, which delivers a finite set of solutions (FS-MPC) [45] and presents a variable switching frequency. The MPC control strategy can be summarized as follows:

- Define a model of the system to be controlled.

- Define a quality or cost function.

Conventionally MPC are used in discrete-time, with a fixed sampling interval  $T_S$ , where the inputs to the system are limited to change only at the discrete sampling instants, i.e.  $t = kT_S$  where  $k \in \{0,1,...\}$  indicates the sampling instants. Then  $\underline{u}(k)$  can be defined as the output of the controller,  $\underline{y}(k)$  as the output of the controlled system and w(k) as the desired or reference value.

The *cost function* is a crucial part of MPC, in this function the predicted system behavior obtained from the model can be penalized e. g. difference between current reference and predicted values. The cost function is minimized at every instant k, over

a finite horizon of length N and the controller calculates a *future* output sequence following this optimization criterion. Thus, the output of the control contains N elements that can be used to control the system.

However, in conventional implementations such as FS-MPC, only the first element is used, i.e. only the k+1 solution is applied. At the next sampling step, i.e. k+1 the whole process is repeated using the latest measured information. The horizon is shifted one step and the optimization process is carried out again. This is called the *receding horizon*, compensating for future disturbances or modeling errors and is presented in Figure 2.10.

Figure 2.10: Receding prediction of horizon, N = 2.

Given that the predicted system output  $\hat{y}(k+1)$  calculated at the instant time t is not equal to the real system output y(k) measured at the instant time t+1 because of these nonlinearities and modeling errors, it is better to start the new prediction from a the measured system output rather than from the predicted process output at the previous sample time. In this sense, MPC introduces a feedback mechanism propagating forward in time the past states of the controlled system [92].

## 2.6.1 Defining the Cost Function

The cost function definition is a crucial stage in the design of a model-based predictive controller, since it allows the selection of the control objectives of the application as well as the required constraints. For power electronic applications the cost function *g* can be described [43] as follows:

$$g = \sum_{i=1}^{n} w_i \cdot ||e_i|| \tag{2.43}$$

$$\|e_i\| = \|x_i^* - x_i^P\|$$

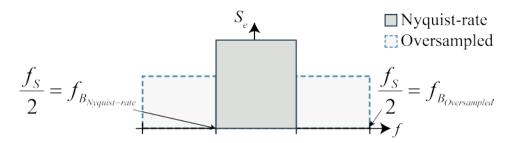

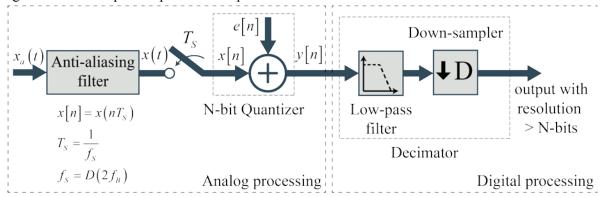

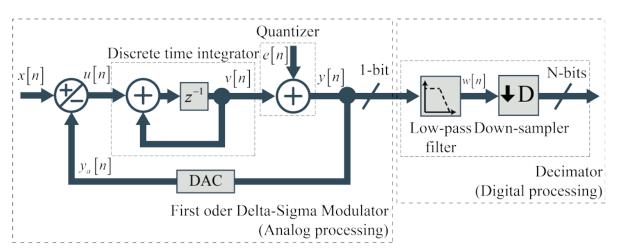

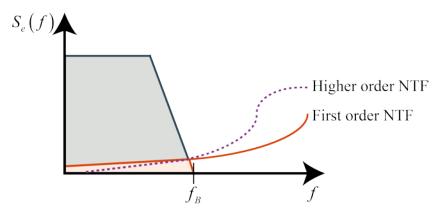

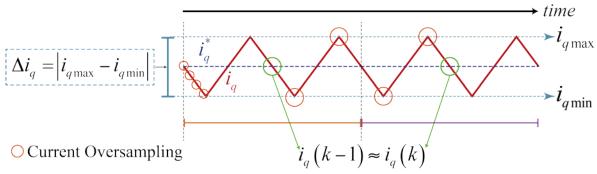

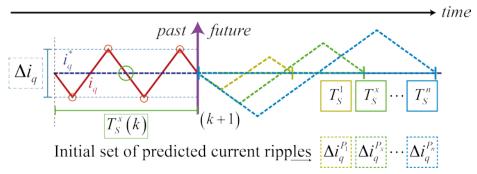

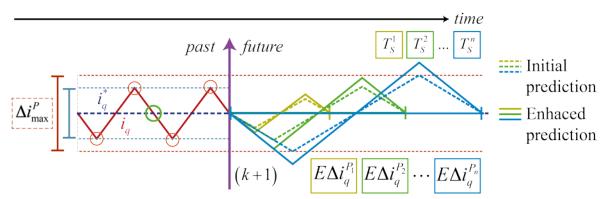

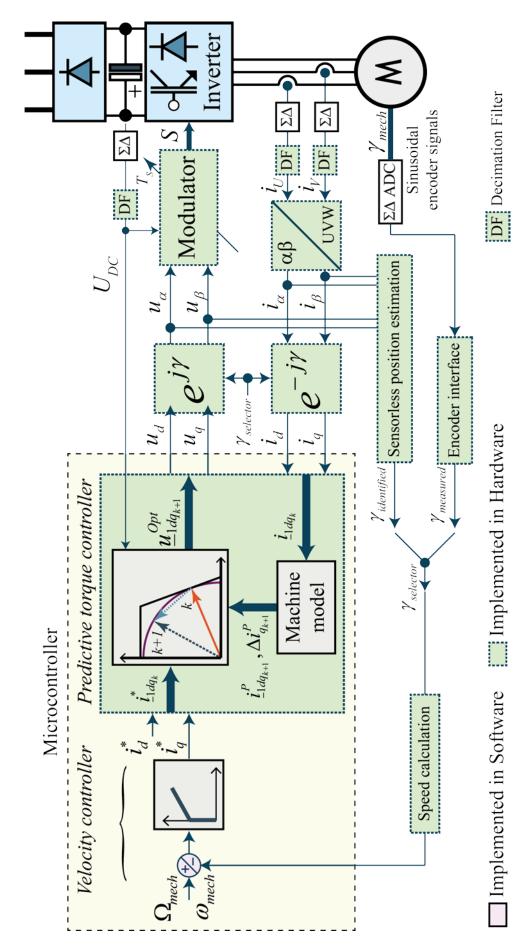

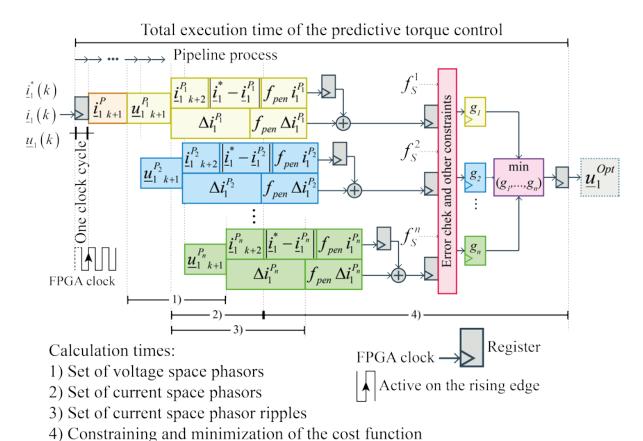

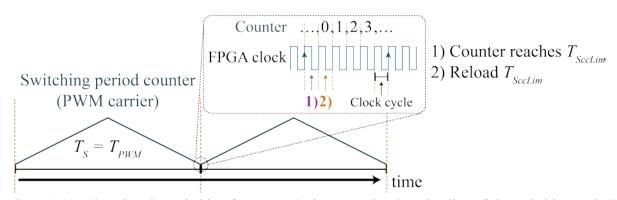

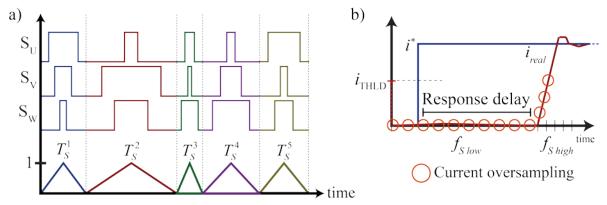

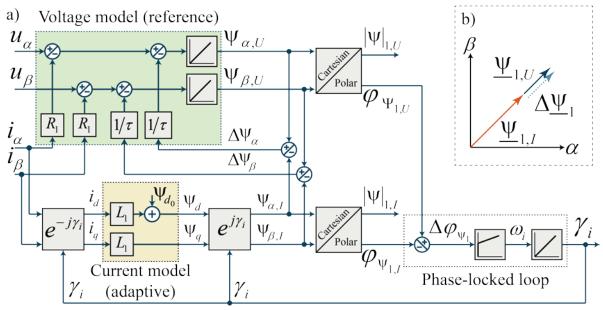

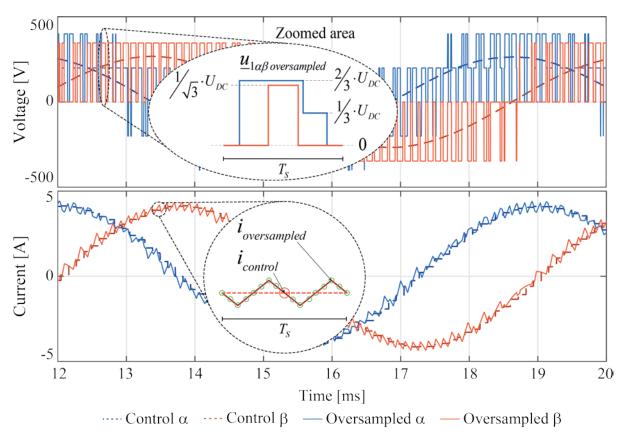

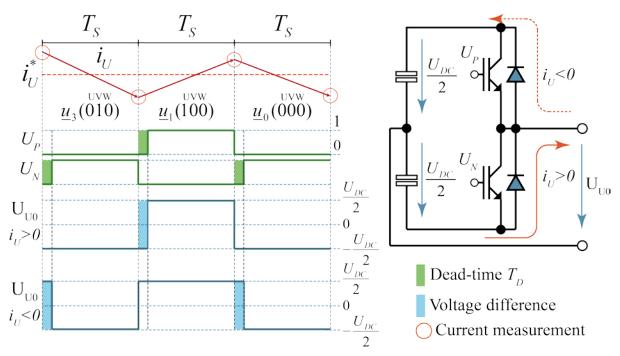

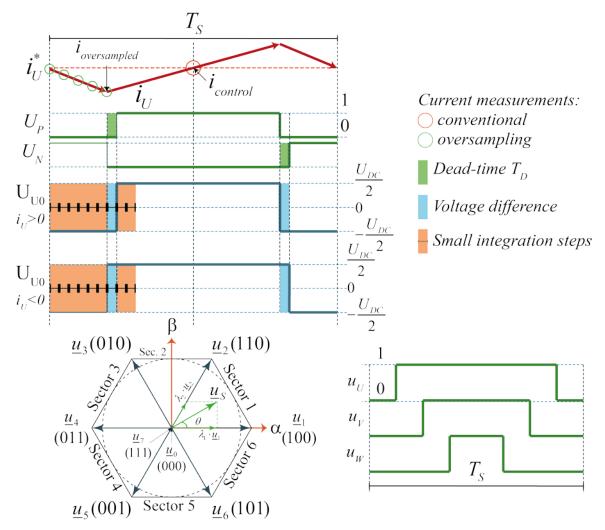

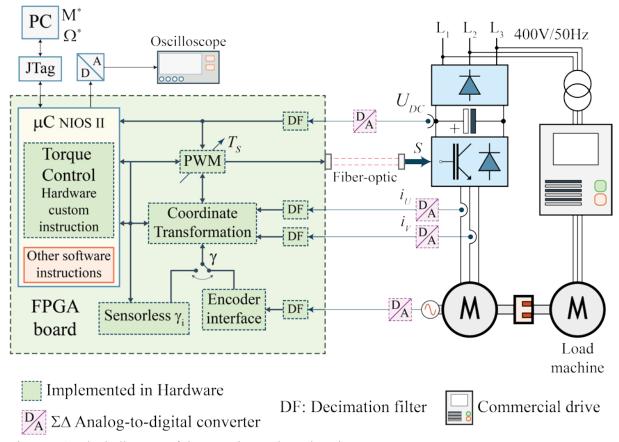

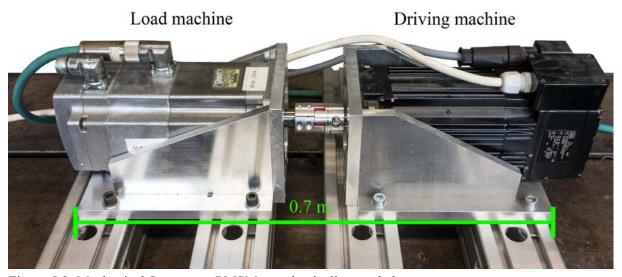

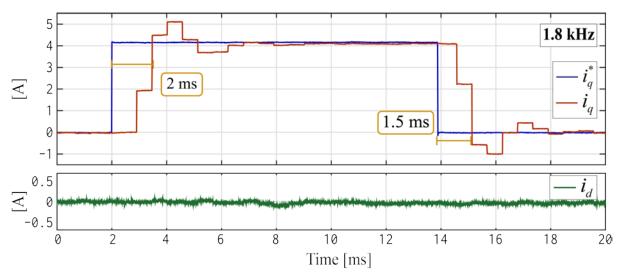

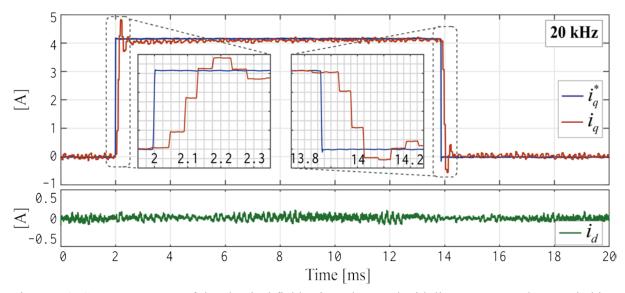

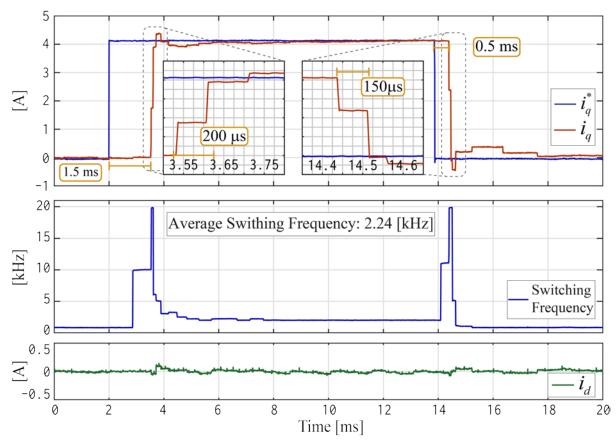

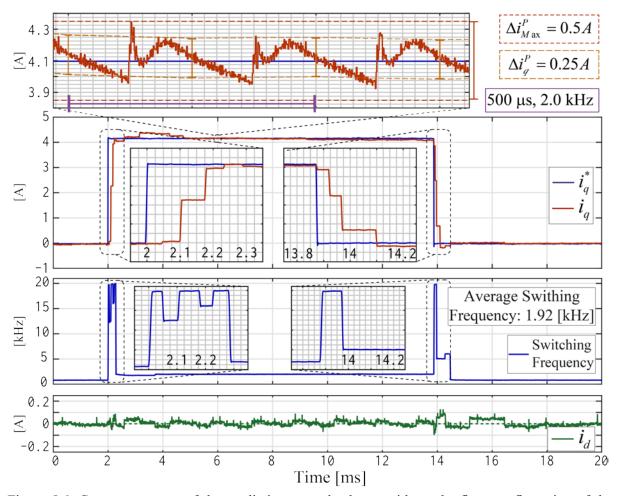

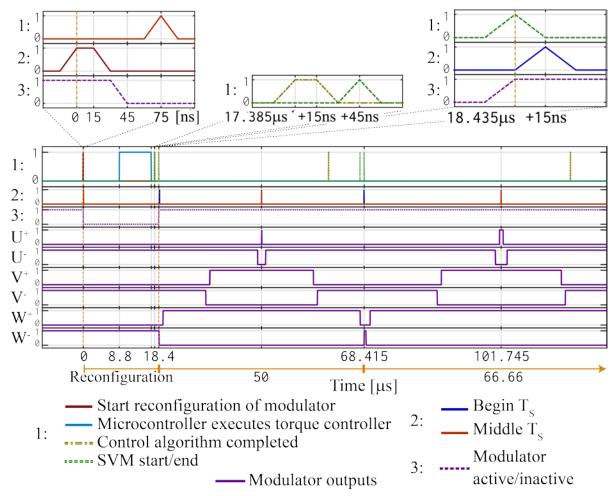

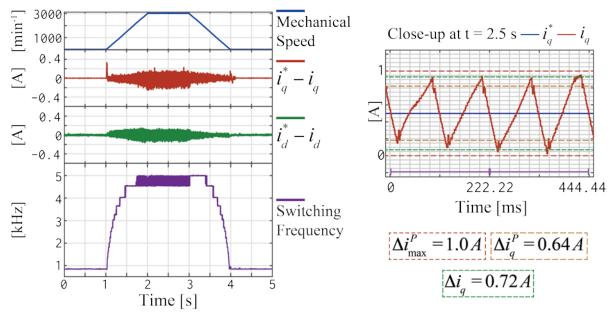

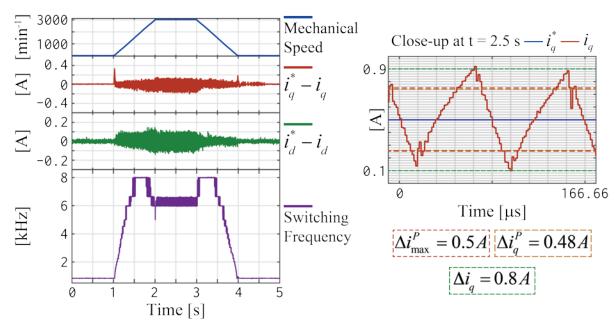

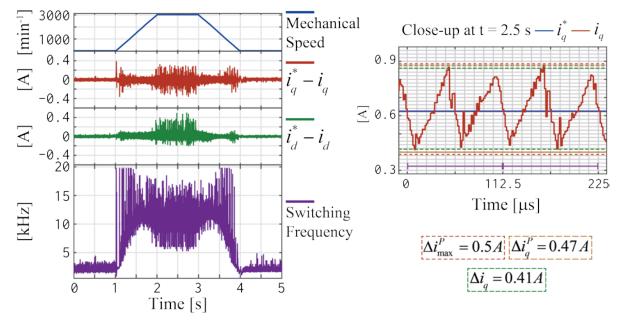

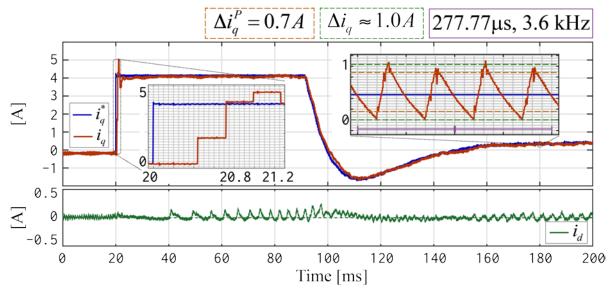

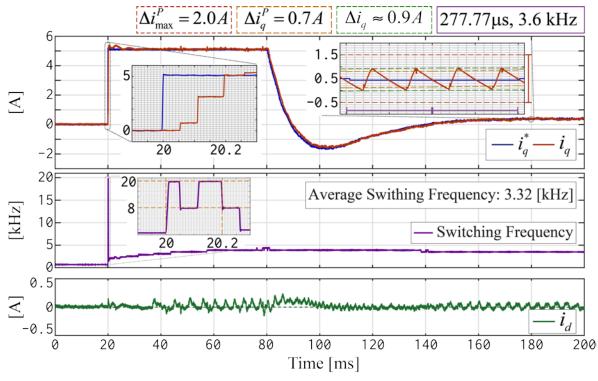

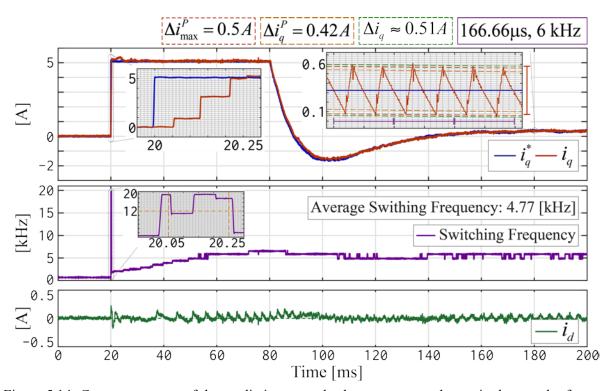

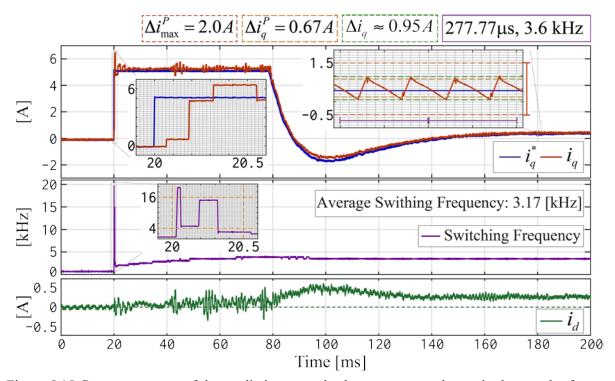

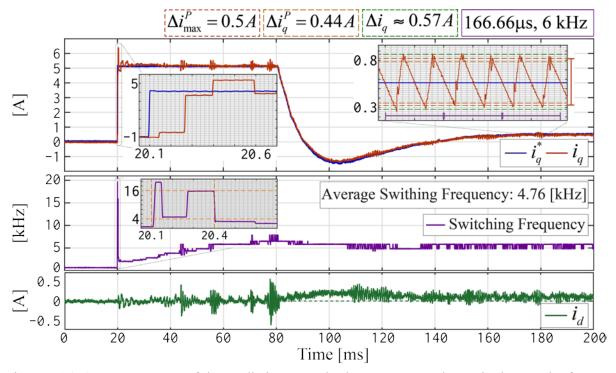

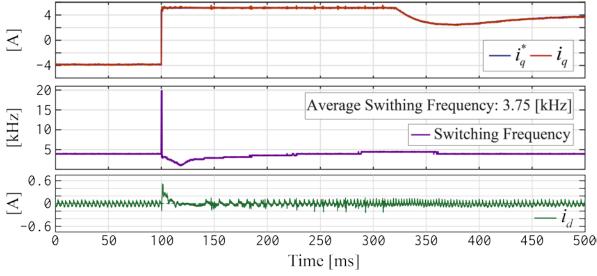

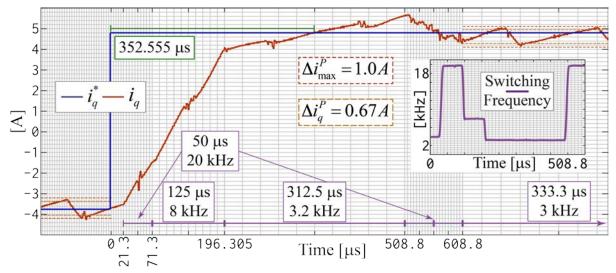

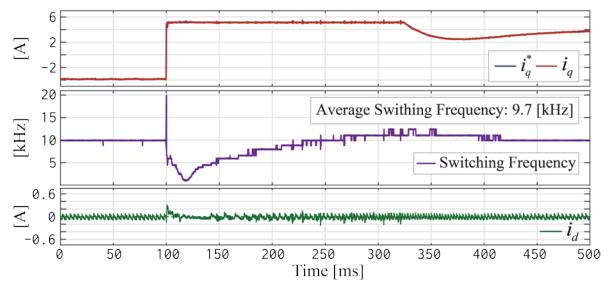

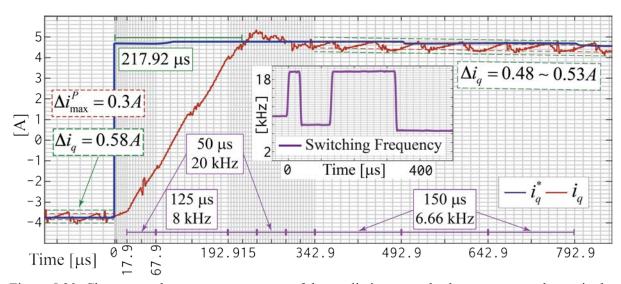

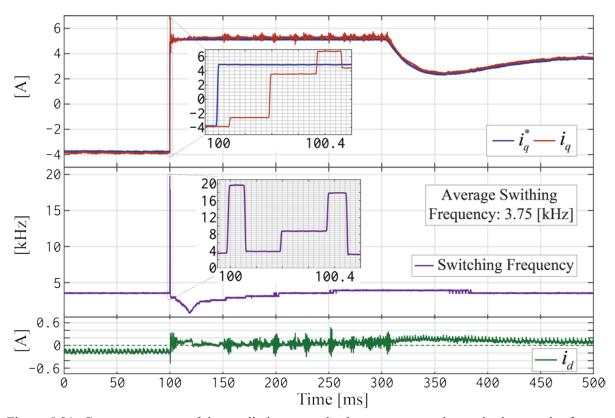

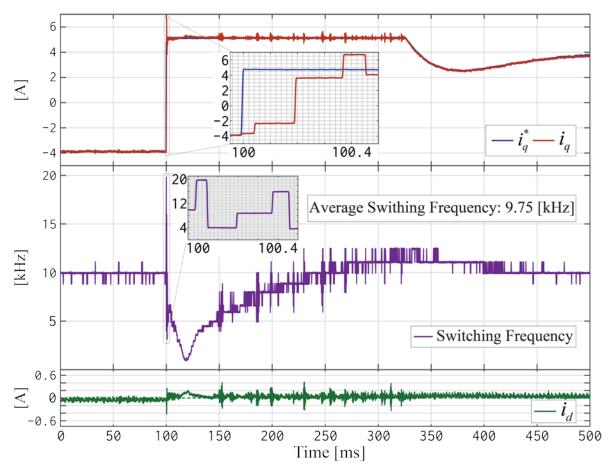

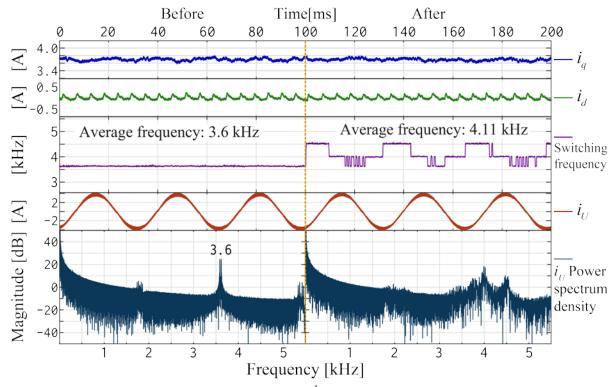

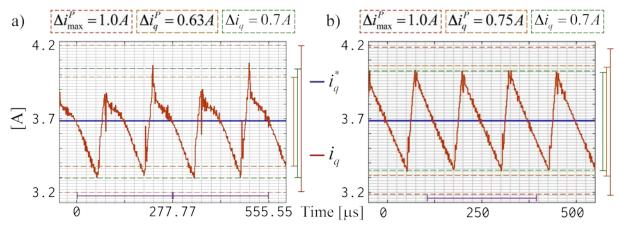

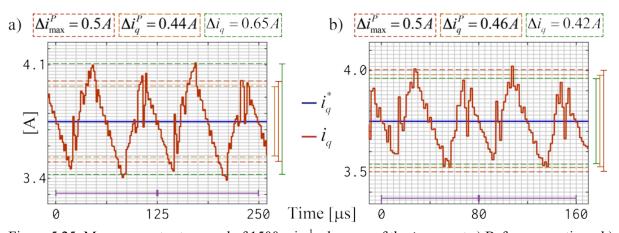

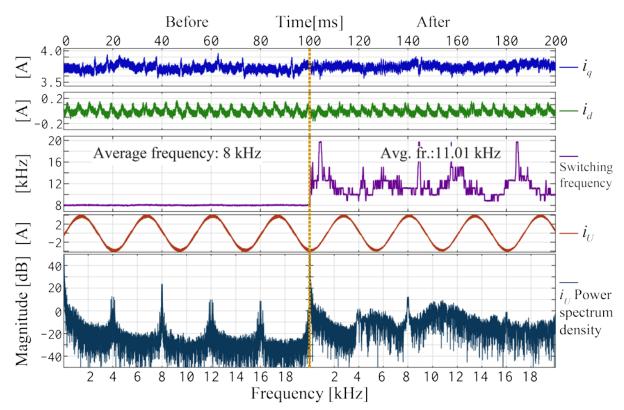

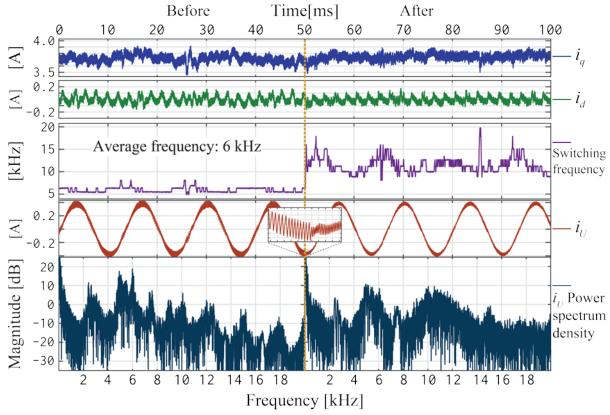

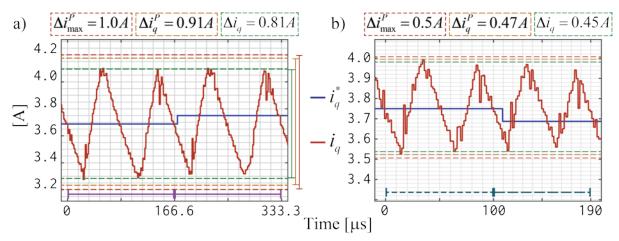

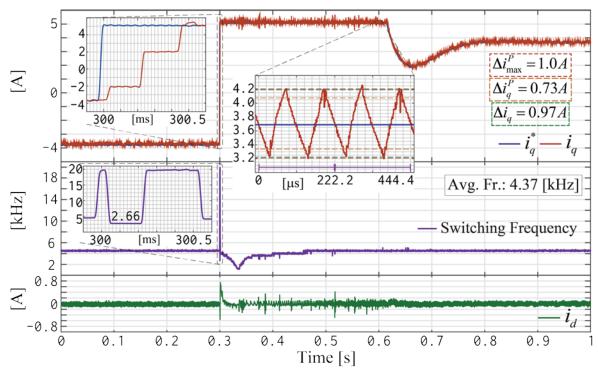

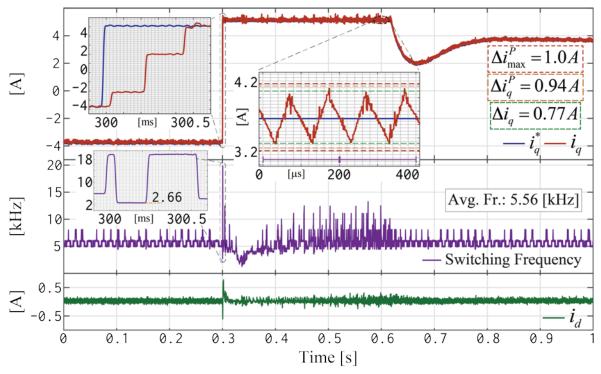

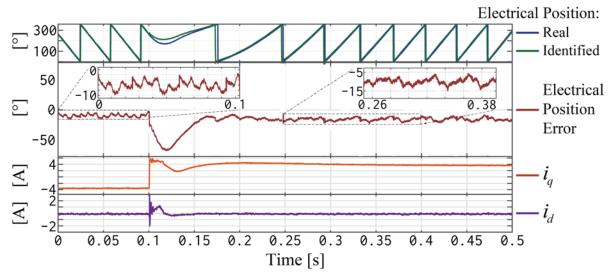

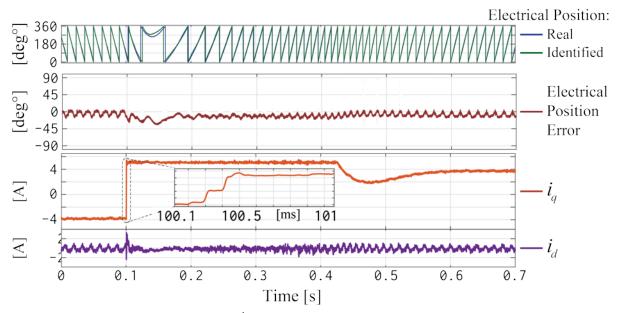

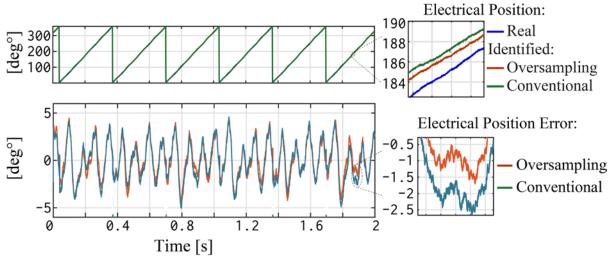

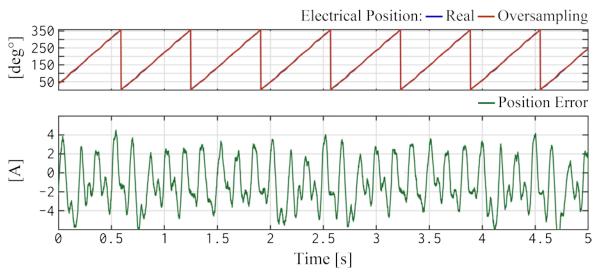

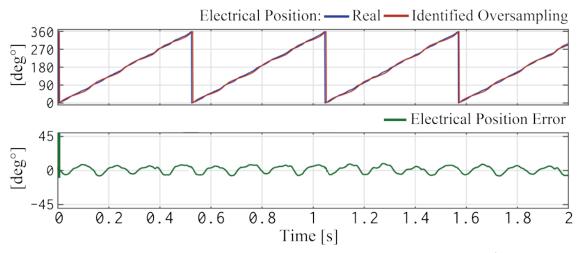

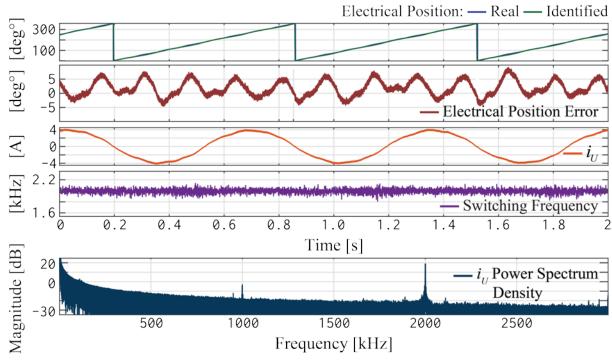

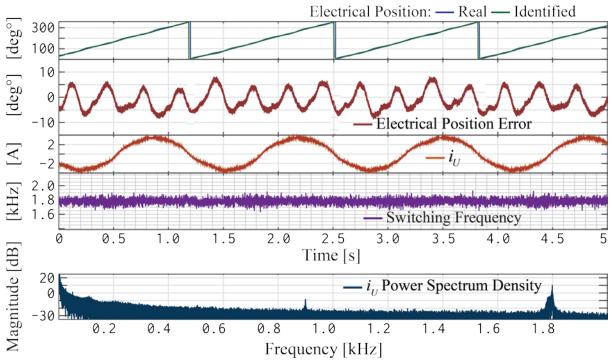

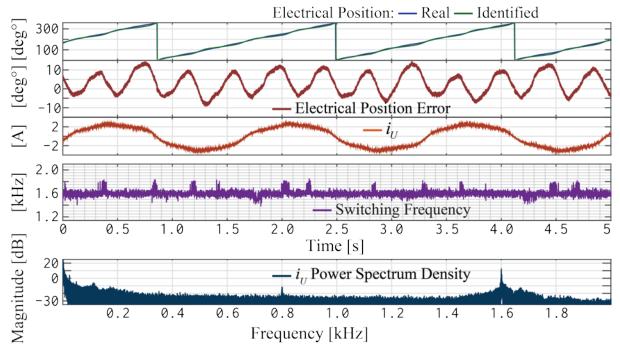

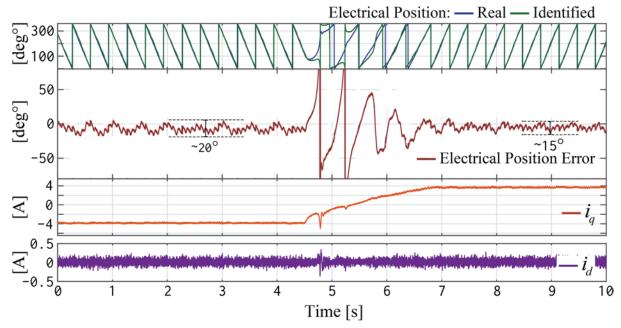

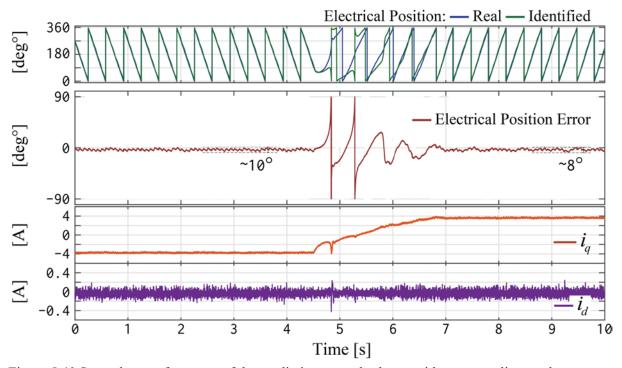

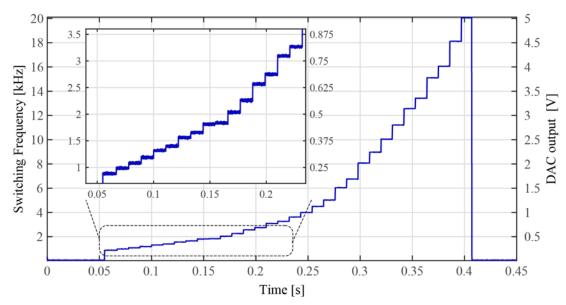

(2.44)